TSMCが次世代ロードマップ公表 A13/A12を29年投入へ:パッケージング戦略も提示(2/2 ページ)

TSMCは、次世代プロセスおよび先進パッケージング技術のロードマップを明らかにした。1.4nm世代の「A14」やその派生プロセス、2nm派生「N2U」に加え、フォトニクス技術や大規模集積を実現するパッケージング戦略を提示。AIデータセンター向けの性能向上と電力効率改善を狙う。

3Dアーキテクチャで大規模集積へ

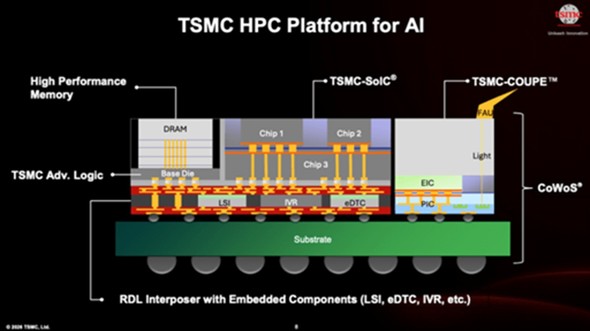

Zhang氏は、TSMCが予測する半導体チップの3Dアーキテクチャの進化を示す図を披露した。

この図は、TSMCが2026年中に生産開始予定の新技術「Compact Universal Photonic Engine(COUPE)」に加え、より高速/高密度なメモリを計算ロジックと統合する手法についても示している。

TSMCは2026年に、レチクルサイズの5.5倍に相当するインターポーザーを導入する予定だ。12個のHBMチップとロジックを統合するために使用するという。

Zhang氏は「2027年には、CoWoSインターポーザーのサイズを9.5レチクルまで拡大し、2028年には14レチクルに拡大する予定だ」と述べる。また同氏は「先進パッケージングが進化し続けていく中で、インターポーザーが制約要因になる可能性がある」と指摘する。

「最終的には、いわゆる『System-on-Wafer(SoW)』を利用し、より多くのロジック/計算装置を統合する予定だ。もはや基板は不要になっていく。300mmウエハー全体で考えると、CoWoSやインターポーザー技術で測定した場合、実質的にレチクルサイズの40倍に相当する」(Zhang氏)

また同氏は「Cerebrasは、SOW技術を最初に採用した企業の1社で、『ややユニークな』推論シリコンを開発している」と述べる。

「Cerebrasは既に、当社のウエハーレベルのインテグレーションを利用して非常に多くのコンピュートダイを統合した。基本的には、ウエハー全体を、全てのダイを統合する基盤として用いることになる。コスト/性能の観点から見て、非常に競争力のある技術だといえる」(Zhang氏)

「CoWoS」不足は終息へ

TSMCは、同社の主要な先進パッケージング技術であるCoWoSの供給不足が、間もなく終息すると見ているようだ。

Zhang氏は「当社のCoWoS生産能力は大きく成長し、現時点で顧客需要に対応可能なレベルに達している」と述べる。

TSMCは引き続き、CoWoSとCOUPEとを組み合わせることで、AIチップにおいてインターポーザーをスイッチングダイにもっと近接させていくとみられる。

「そうすることで、レイテンシをさらに2分の1に低減でき、同時に電力効率も約2.5倍向上する。これは、将来的にAIアプリケーション向けの高性能なチップ間通信を実現すべくわれわれが開発を進めている、究極のインテグレーション技術だ」(Zhang氏)

TSMCは、1年以上前にシリコンフォトニクス事業に参入した、GlobalFoundriesやTowerなどの小規模ファウンドリーに追従する形になる。

TSMCは引き続き、半導体チップ1世代ごとに、30%のエネルギー効率向上を実現できるとみているようだ。Zhang氏は「われわれは2年毎に30%の高効率化を実現している」と述べる。さらに、「TSMCのチップを使用するAIデータセンターでは、必ずしもこれと同様の高効率化を実現できるわけではない」と付け加えた。

同氏はEE Timesの取材に対して「データセンターレベルでは、数十万規模のGPUやAIアクセラレーターを接続する場合、大量の追加コンポーネントが必要になる。スイッチや電源供給管理など、さまざまなものが必要だ。全体的な電力面でのメリットは、最終的にデータセンターレベルで測定しなければならないのは明白だ」と述べる。

Hutcheson氏は「TSMCは立て続けに発表を行っているが、それは必ずしも新しいプロセスノード投入の加速を示すわけではない」と指摘する。

「同社が、実際に新しいノードの導入ペースを加速させているのかは分からない。新ノードのリリースについて、自信を持ってよりオープンになってきているからではないだろうか。業界は近年、シンプルなスケーリングに加え、GAAや裏面電源、新材料など、さまざまなプロセスの複雑性に対応しなければならなかった。これをうまく管理できるようになり、ロードマップのリリースにもさらに自信を持てるようになったのだろう」(Hutcheson氏)

【翻訳:滝本麻貴/田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

中東情勢に伴うヘリウム(He)とナフサの供給危機問題を解説するシリーズ。今回は、製造装置メーカーとチップメーカーへの波及経路をたどりながら、短期〜中長期的な影響を推測する。さらに、政府による「ナフサ4カ月在庫」議論が“的外れ”である理由を述べる。 560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

TSMCの2026年の設備投資額は560億米ドルに達する見込みだ。それでも、AI半導体の旺盛な需要に応えるには不十分だという。 ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

米国とイスラエルによるイラン攻撃に端を発した中東問題は、半導体業界にも多大な影響をもたらす。その最たるものがヘリウム(He)の供給停止だ。本稿では、ヘリウム調達停止が半導体業界に与える影響を前後編に分けて詳細に解説、考察する。【訂正あり】 TSMCが熊本第2工場で3nm導入へ CEOが表明

TSMCが熊本第2工場で3nm導入へ CEOが表明

TSMCは熊本県に建設を進めている熊本第2工場において、3nmプロセスを導入すると表明した。2026年2月5日、同社会長兼CEOであるC.C.Wei氏が日本の総理大臣官邸を訪問し高市早苗首相に伝えた。 TSMCは2nmで主導権維持、SamsungとIntelに勝機はあるか

TSMCは2nmで主導権維持、SamsungとIntelに勝機はあるか

米国EE Timesが調査した複数のアナリストによると、TSMCは、最近生産開始を発表した2nmプロセスによって、今後数年にわたって高度な半導体ノードでライバルのSamsungとIntelを凌ぐ見込みだという。