三重富士通、SuVoltaから低消費電力トランジスタ技術の知的財産権を取得――40nm、フラッシュ混載へ応用:ビジネスニュース 企業動向

三重富士通セミコンダクターは2015年4月、米SuVoltaから低消費電力CMOS技術に関する知的財産権を取得したと発表した。従来、SuVoltaからライセンス供与を受けて55nmプロセスに適用してきた同技術を、40nmプロセスなどへと展開していく。

三重富士通セミコンダクターは2015年4月8日、米SuVoltaから低消費電力CMOS技術に関する知的財産権を取得したと発表した。取得金額は明らかにしていない。今回の知的財産権取得により、従来、SuVoltaからライセンス供与を受けて、55nmプロセスに適用してきた同技術を、40nmプロセスなどに展開していく。

同じ回路であれば最大50%抑制

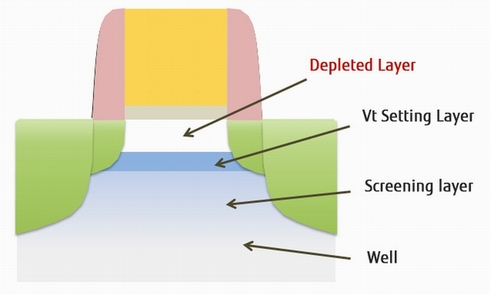

三重富士通セミコンが取得したのは、Deeply Depleted Channel(DDC)トランジスタからなる低消費電力CMOS技術「PowerShrink」に関する知的財産権だ。DDCトランジスタは、しきい値(Vt)ばらつきを抑制し、キャリア移動度を高められるなどの特長を持つSuVolta独自のトランジスタ技術で、リーク電流、動作時消費電力を抑えることができる。従来型のトランジスタと、同じ規模/処理スピードの回路と比べ最大50%の消費電力を削減できるとする。

取得により、40nm/フラッシュ混載などへの応用を加速へ

三重富士通セミコンは、SuVoltaと共同で、自社の製造プロセス技術と組み合わせる技術開発を行い、2013年9月からSuVoltaからライセンスを受ける形で、PowerShrink技術を採用した55nmプロセスによるLSI製造を手掛けてきた。

今回の知的財産権の取得により、55nmプロセスでのさらなる低消費電力化に向けた技術開発を行う他、PowerShrink技術を現在、UMCの出資を受けるなどして対応を進めている40nmプロセスへ展開する方針。さらに、既に確立しているフラッシュメモリとの混載技術*1)なども生かし、不揮発メモリ素子やRF素子と組み合わせたプラットフォームの構築を目指す。同社では「従来のLP(Low Power)プロセスに比べ、リーク電力が1/1000となる“Extreme Low Power”プラットフォーム構築によって、同じプロセス世代で世界一の超低消費電力技術を提供することで、顧客製品の市場競争力と性能向上を実現する」としている。

*1)関連記事:DDCトランジスタとフラッシュメモリの混載技術、富士通セミコンが開発

三重富士通セミコンダクターは、2014年12月に設立された富士通セミコンダクターの子会社。300mmウエハー製造ラインを活用した半導体受託製造専門企業として事業を展開している*2)。

*2)関連記事:“日本のピュアファウンドリ”に本気で挑む三重富士通の勝算

関連キーワード

消費電力 | 富士通 | トランジスタ | IPR(知的財産権) | 富士通セミコンダクター | 企業動向(エレクトロニクス) | ビジネスニュース(EE Times Japan) | プロセス技術(エレクトロニクス)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

“日本のピュアファウンドリ”に本気で挑む三重富士通の勝算

“日本のピュアファウンドリ”に本気で挑む三重富士通の勝算

富士通の半導体事業再編の中で2014年末に誕生したファウンドリ専業会社「三重富士通セミコンダクター」。台湾をはじめとした海外勢の独壇場となっている大口径の300mmウエハーによる半導体受託生産市場で、最先端微細加工技術、大きな生産能力を持たない同社はどう生き残って行くのか。同社社長の八木春良氏に聞いた。 DDCトランジスタとフラッシュメモリの混載技術、富士通セミコンが開発

DDCトランジスタとフラッシュメモリの混載技術、富士通セミコンが開発

富士通セミコンダクターは、DDC(Deeply Depleted Channel)技術を適用したロジック回路とフラッシュメモリセルを同一チップに混載し、同社三重工場の55nmプロセスで製造できる技術を開発したと発表した。これまで高温でのプロセス処理が必要とされてきたフラッシュメモリセルを、低温プロセスのみで形成することに成功したことで、ロジック回路との混載を可能とした。 ルネサス、2015年度内にSOTB採用マイコンを製品化へ――消費電力1/10以下、0.4V駆動品も可能に

ルネサス、2015年度内にSOTB採用マイコンを製品化へ――消費電力1/10以下、0.4V駆動品も可能に

ルネサス エレクトロニクスは2015年度(2016年3月期)中にも新型トランジスタプロセス技術「薄型BOX-SOI(SOTB:Silicon-on-Thin-Buried Oxide)」を用いたマイコンを製品化する。同技術を用いることで、0.4Vという超低電圧駆動のマイコンが実現できるという。 富士通三重工場にUMCが100億円出資――40nmライン新設し車載向け製品を生産へ

富士通三重工場にUMCが100億円出資――40nmライン新設し車載向け製品を生産へ

富士通セミコンダクターは2014年8月29日、新設予定の三重工場(三重県桑名市)を運営するファウンドリ会社に台湾のUMCが100億円を出資することで基本合意した。同時に、UMCの40nm LP(Low Power)プロセス技術を富士通セミコンにライセンス供与し、同工場に40nmプロセス製造能力を構築することでも基本合意した。 ルネサス、28nm世代混載フラッシュ技術を改良――順調に進む次世代車載マイコン開発

ルネサス、28nm世代混載フラッシュ技術を改良――順調に進む次世代車載マイコン開発

ルネサス エレクトロニクスは2015年2月25日、28nmプロセス世代の車載マイコン向けに、高速読み出し、高速書き換えを実現する新たな混載フラッシュメモリ技術を開発したと発表した。