IoT時代のサーバを助ける56Gbps送受信回路:消費電力は従来と同じで2倍高速に(2/2 ページ)

富士通研究所とソシオネクストは、サーバ間の光通信向けに、56Gビット/秒の通信速度を実現する送受信回路を発表した。ソシオネクストは今回、オプティカルネットワーク分野で培ってきたノウハウを活用することで、消費電力を削減できる新しいタイミング誤差検出方式を開発。これにより、現行と同じ消費電力で2倍高速となる56Gbps送受信回路を実現している。

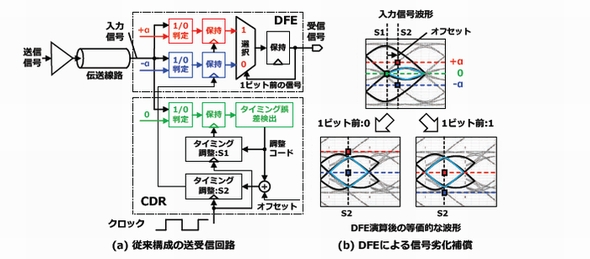

現行の送受信回路の仕組み

現行の送受信回路において、DFEは伝送経路によって劣化した波形を入力として、異なるしきい値+αと−αを持った別々の判定回路で判定している。その結果について、1ビット前に処理したビット値が0であれば−α、ビット値が1であれば+αのしきい値を持った判定回路の結果を選択することで劣化した信号を補償する。

CDRは、入力信号を観測することで、入力信号の波形が最大の振幅になったときにDFEが信号を取り込めるように、DFEの動作タイミングを調整している(図1)。

同IP開発部マネジャーの東裕人氏は、「従来はデータの遷移点(バウンダリー)と復元した情報の2つのデータをCDRに送り、遷移点に対して位相が速いか遅いかをモニターしてフィードバックをかけていた」と語る。

入力信号が100または011になるときだけ

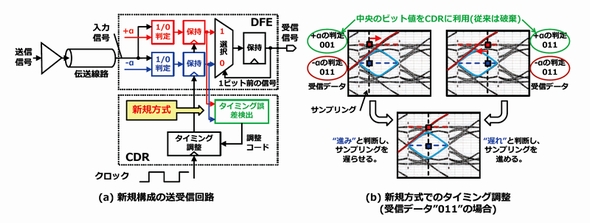

仲氏は、「今回開発した技術は、復元する情報の“取り方”を変えた。DFEが見ている縦方向の電圧の情報を使って、動作タイミングの進み/遅れをうまく見つけ出すことに成功した。これにより、回路の物量もそれほど増えず、周波数も内部では上がっていないが、消費電力を上げずに2倍のデータレートを実現できた」と語る。

具体的には、DFE演算後の波形を分析した結果、連続する3ビットの入力信号が「100」または「011」となる場合において、DFEの2つの判定回路の結果を比較することでDFEの動作タイミングの進み/遅れを検出できることが分かったとする。同社は、この結果にもとづき、連続する3ビットの入力信号が100または011になるときだけ、タイミングを検出する新しい方式を開発(図2)。これにより、バウンダリー制御を行っていたCDRのタイミング判定回路を削減でき、クロック線などの配線も不要になった。

同IP開発部で、今回受信側部分の開発を行った工藤真大氏は、「CDRのクロックリカバリーの方式が従来と違い、その作り込みや動作の検証が難しかった」と語った。

56Gビット/秒以外にも適用範囲を

富士通研究所とソシオネクストは今後、今回開発した技術をサーバやスイッチの半導体チップと光モジュール間のインタフェース部などに適用し、2018年度の実用化を目指すとしている。「今回は、コンセプトの検証をしっかり行うことができた。次は、いかにロバストで産業製品に使用できるかが課題になる。検証を重ねて製品として使用できるレベルに持っていき、56Gビット/秒以外にも適用範囲を広げたい」(仲氏)とした。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

2時間映画も10秒で――WiGigを体験してきた

2時間映画も10秒で――WiGigを体験してきた

パナソニックと成田国際空港は2016年2月18日、次世代無線通信規格「WiGig」を使用したWiGigスポットの実証実験を開始した。最大伝送速度7Gビット/秒でWi-Fiよりも10倍以上速いというWiGigとは一体何なのだろうか。本記事は、実証実験の様子を写真や動画で紹介する。 人の“模倣”ではないAIで、未来を作る

人の“模倣”ではないAIで、未来を作る

NTTは、「R&Dフォーラム 2016」の一般公開を前に、主な展示をプレス向けに紹介した。AI(人工知能)を搭載した“ぶつからないクルマ”や、眼球の動きから“好みのタイプ”を判別する技術、VR(仮想現実)を利用したスポーツトレーニングのデモなどが披露された。 300GHz帯の無線通信技術を開発、伝送速度100Gb/秒

300GHz帯の無線通信技術を開発、伝送速度100Gb/秒

情報通信研究機構(NICT)は、広島大学とパナソニックと共同で、テラヘルツ波(300GHz帯)を用いた、伝送速度100Gビット/秒を超えるデジタル情報の無線伝送を可能にする技術の開発に成功したと発表した。NICTによると、同技術の実現は「世界で初めて」という。 半径3μmでシリコン光導波路を曲げる技術

半径3μmでシリコン光導波路を曲げる技術

産業技術総合研究所(以下、産総研)は2016年1月28日、シリコン光配線の先端を小さな曲げ半径で垂直方向に立体湾曲させる技術を開発したと発表した。シリコン光回路のウエハー面に対し垂直な方向で光を入出力できるため、光ファイバーや光部品と容易に結合できるようになる。