「SEMICON West 2016」、Synopsysが予測する5nm世代のトランジスタ技術:福田昭のデバイス通信(93)(2/2 ページ)

Synopsysの講演では、5nm世代のトランジスタのシミュレーション評価結果が報告された。この結果からはFinFETの限界が明確に見えてくる。5nm世代に限らず、プロセスの微細化が進むと特に深刻になってくるのが、トランジスタ性能のばらつきだ。

FinFETの限界とシリコンナノワイヤの可能性

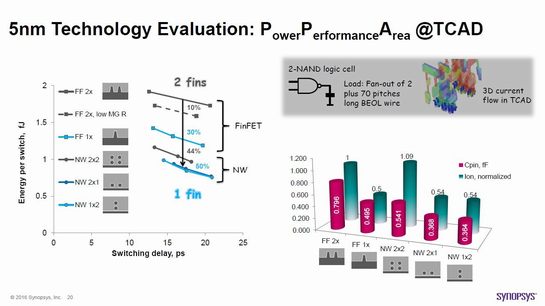

5nm世代におけるロジック用トランジスタでPPA(Power, Performance, Area)をシミュレーターのTCAD(Technology CAD)によって評価すると、FinFETの限界が明確に見えてくる。

入力数2、ファンアウト2、負荷配線長70ピッチのNANDゲート論理セルで、3次元の電流経路をTCADでシミュレーションした。FinFETでフィンの数(最小単位)を2枚から1枚に減らすと、スイッチングに必要なエネルギーは30%ほど低下する。

FinFETではなく、シリコンナノワイヤにFET構造を換えると、スイッチングに必要なエネルギーはさらに低下する。例えば2本×2本のナノワイヤ(NW)FETだと、2枚フィンのFinFETに比べ、スイッチングに必要なエネルギーは44%ほど下がる。ナノワイヤの本数を2本に減らすと、2枚フィンのFETに比べて約50%にスイッチングエネルギーが減る。一方、スイッチングの遅延時間はほとんど変わらない。

トランジスタのオン電流は、2枚フィンのFinFETを1.00とすると、2本×2本のナノワイヤFETでは1.09でほぼ同じ電流駆動能力を備える。これに対して1枚フィンのFETと2本ナノワイヤのFETでは0.5前後となり、電流は半分に低下してしまう。

ひどくなる「ばらつき」との闘い

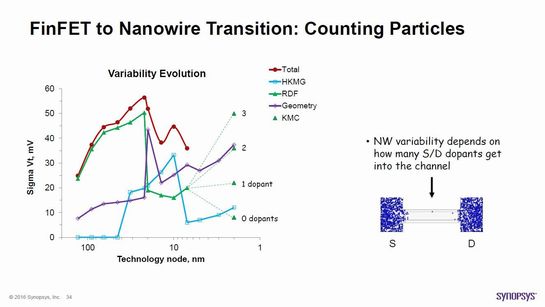

トランジスタの微細化とは「ばらつき(Variability)」との闘いでもある。大規模な集積回路では、膨大な数のトランジスタを製造する。トランジスタの性能にはばらつきがある。集積回路の性能を決めるのは、トランジスタの最高性能ではなく、中心的な性能でもない。最も遅いトランジスタが集積回路の性能を決める。中心的な速度が高くても、ばらつきが大きければ集積回路の性能は、中心的な速度がやや低くてもばらつきが非常に小さな集積回路に比べて劣ってしまう。

45nm世代から32nm世代に移行するときは、HKMG(高誘電率ゲート絶縁膜と金属ゲート電極)技術を採用してばらつきの増加を押さえ込んだ。これまでの多結晶シリコンゲートによるばらつきがなくなったことが大きく効いた。22nm世代から14nm世代に移行するときは、FinFET技術を導入してばらつきを低減した。RDF(Random Dopant Fluctuation)によるばらつきが大幅に小さくなることが寄与する。

10nm世代では、HKMGの金属ゲートがばらつきの主要因となる。7nm世代ではアモルファスの金属ゲートを導入することで、ばらつきを大幅に小さくできる。

5nm世代では、どうなるのか。FinFETとナノワイヤFETは、プレーナ型のMOSFETに比べると、ジオメトリ(形状)の影響を受けやすい。ナノワイヤFETはFinFETに比べるとゲート長(L)の変動による影響は小さいものの、ゲート幅(W)の変動による影響を受けやすい。

またナノワイヤFEDでは、理想的にはチャンネル(ナノワイヤ領域)にはドーピング原子が存在しない。しかしソース領域あるいはドレイン領域のドーピング原子(ドーパント)が漏れて1個でもナノワイヤ領域に入り込むと、しきい電圧が大きく変動してしまう。

微細化の進展(横軸)としきい電圧のばらつき(縦軸)の推移。なお図中のKMCとは動的モンテカルロ(Kinetic Monte Carlo)シミュレーションのこと。Synopsysの講演スライドから(クリックで拡大)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(Samsung編)

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(Samsung編)

Samsung Semiconductorの講演では、「ムーアの法則」の現状認識から始まり、同社が考える微細化のロードマップが紹介された。Samsungは28nm世代と10nm世代が長く使われると予想している。さらに同社は、EUVリソグラフィが量産レベルに達するのは2018年で、7nm/5nm世代のチップ製造に導入されるとみている。 EUVは、微細化の“万能策”ではない

EUVは、微細化の“万能策”ではない

半導体製造プロセスの微細化を進めるには、EUV(極端紫外線)リソグラフィーが鍵になるといわれている。ばく大な資金が、同技術の開発に投入されているが、その進捗は必ずしも期待通り、予定通りではないようだ。 Intel、「ムーアの法則は微細化の実現ではない」

Intel、「ムーアの法則は微細化の実現ではない」

「ISPD 2016」においてIntelは、10nmプロセス以降もCMOSに注力する考えであることを明らかにした。同社はそこで、ムーアの法則は微細化そのものというわけではなく、より多くのダイをウエハー上に形成することで利益を確保することだと、述べている。 スピン注入型MRAMの微細化(スケーリング)

スピン注入型MRAMの微細化(スケーリング)

STT-MRAMの記憶容量を拡大する最も基本的な方法が、微細化だ。現時点でSTT-MRAMは、研究レベルでかなりのレベルまで微細化できることが分かっている。実際の研究結果を交えて紹介しよう。