SanDiskが語る、ストレージ・クラス・メモリの概要:福田昭のストレージ通信(44) 抵抗変化メモリの開発動向(3)(2/2 ページ)

ストレージ・クラス・メモリ(SCM)は、次世代の半導体メモリに最も期待されている用途である。今回は、このSCMの要件について、記憶密度やメモリアクセスの制約条件、メモリセルの面積の観点から紹介する。

ランダム・アクセスが必須とは限らない

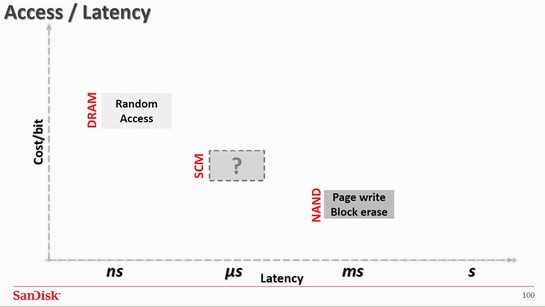

メモリアクセスの制約条件についてもふれておかなければならない。NANDフラッシュメモリは、ランダムなアクセスが可能なメモリ(RAM)ではない。書き換えのアドレスアクセスに制約があり、なおかつ、書き換えは消去(イレーズ)と書き込み(ライト)の2段階の動作を必要とする。消去はブロック単位(数メガバイト単位)、書き込みはページ単位(数十Kバイト単位)である。

これに対してDRAMは読み出し、書き換えともにランダムなアクセスが可能なメモリである。SCMは、当然ながら、ランダムなアクセスが可能なメモリであることが望ましい。ただし、コストを大幅に下げるためにアクセスに制約が加わったとしても、許容される可能性はある。

メモリセルアレイの積層構造でコストを下げる

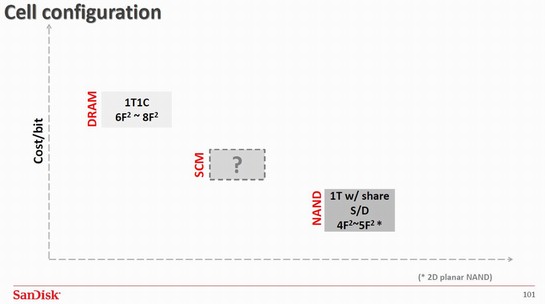

メモリセルのアーキテクチャとセル面積の関係にも留意すべきだろう。よく知られているように、DRAMのメモリセルは1個のメモリセル選択用トランジスタ(MOSFET)と1個の記憶素子(キャパシター)で構成される。NANDフラッシュメモリのメモリセルは、1個の記憶用MOSトランジスタが隣接する記憶用MOSトランジスタとソースおよびドレインを共有する。

設計ルール(フィーチャーサイズ)をFとすると、メモリセルの大きさは、N(数値)×(Fの2乗)で表記することが多い。F2に換算するのは微細加工寸法の影響を避けるためである。

DRAMのメモリセルは、6F2〜8F2の大きさがある。一方でNANDフラッシュメモリのメモリセルはかなり小さく、4F2〜5F2にとどまる。この数値はプレーナ技術の場合で、3D NAND技術を採用したNANDフラッシュでは、ずっと小さくなる。

SCMに望まれるのは、メモリセルの大きさを6F2よりも小さくすることだ。これは実際にはかなり難しく、メモリセルアレイを積層した2層以上の立体構造が必要となる可能性が高い。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

2016年の半導体市場、DRAMの回復で成長の見通し

2016年の半導体市場、DRAMの回復で成長の見通し

IC Insightsによると、半導体IC市場はDRAMが回復基調にあることを受け、2016〜2017年にかけて、それぞれ1%、4%の売り上げ成長率を達成するという。 4DS Memoryが40nmプロセス適用のReRAMを開発

4DS Memoryが40nmプロセス適用のReRAMを開発

オーストラリアの4DS Memoryが、40nmプロセスを適用したReRAMを開発した。モバイルクラウドの分野をターゲットとする。 次世代不揮発メモリ、まずは出荷を――Everspin

次世代不揮発メモリ、まずは出荷を――Everspin

次世代不揮発メモリは幾つか候補はあるものの、実用化には至っていないものも多い。MRAM(磁気抵抗メモリ)メーカーEverspin TechnologiesでCEOを務めるPhillip LoPresti氏は、“完成形”にこだわらず、まずは量産して市場に投入することが重要だと主張する。 Samsung、スマホ業績の悪化を半導体事業が補てん

Samsung、スマホ業績の悪化を半導体事業が補てん

Samsung Electronicsの2016年第3四半期の業績は、スマートフォンの事業は大幅に悪化したものの、好調な半導体事業がそれを補う形となった。