MRAMの書き込みエラー率、新型回路で低減:電圧トルクMRAM実用化へ

東芝と産業技術総合研究所(産総研)は、不揮発性磁気メモリ(MRAM)のための新たな電圧駆動書き込み方式を開発した。消費電力が極めて小さい高速メモリ「電圧トルクMRAM」の実用化に弾みをつける。

プロセッサ用ラストレベルキャッシュの大容量化が可能に

東芝 研究開発センターの藤田忍研究主幹と産業技術総合研究所(産総研)スピントロニクス研究センターの野崎隆行研究チーム長らによる研究開発チームは2016年12月、不揮発性磁気メモリ(MRAM)のための、新たな電圧駆動書き込み方式を開発したと発表した。「電圧トルクMRAM」の書き込みエラー率を低減するための回路技術であり、実用化に弾みをつける。

研究開発チームはこれまで、電圧駆動型磁気メモリ「電圧トルクMRAM」を実現するために、高速パルス電圧によって磁化反転を制御する磁気トンネル接合素子(MTJ素子)の開発などに取り組んできた。ところが電圧トルクMRAMは、従来の電流駆動型磁気メモリ(STT-MRAM)に比べて駆動電力は小さいが、情報の書き込みエラー率が大きいなど、実用化に向けては課題もあった。

研究開発チームは、書き込みエラー率として10-10〜10-15を実用化のメドとして、これらを実現するための材料開発などに取り組んできた。今回は、書き込み時のパルス電圧の形状を工夫し、疑似的に材料特性を向上させることで書き込みエラー率を低減する手法の開発に成功し、それを実現するための回路を新たに設計した。

電圧による情報書き込み動作において、磁化反転が起きる前の初期状態(始状態)および、反転後の終了状態(終状態)で、熱エネルギーの影響を受けることにより、磁化の向きに揺らぎが生じていた。この揺らぎが大きくなるほど、書き込みエラー率が増大するという。つまり、書き込みエラー率を低減するためには、始状態と終状態における磁化の熱揺らぎを、いかに抑制するかが課題となっていた。

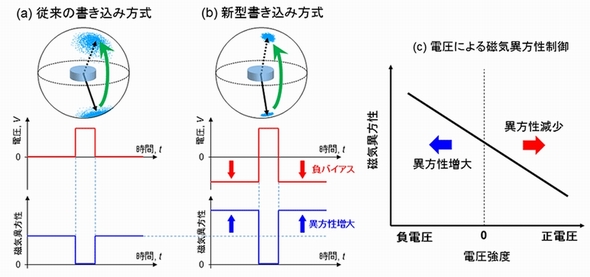

そこで研究開発チームは、電圧を用いて疑似的に垂直磁気異方性を増大させて書き込みエラー率を低減する手法を開発した。電圧による磁気異方性の変化をみると、正電圧では磁気異方性が小さくなり、負電圧では大きくなる。新たに開発した手法では、始状態と終状態で負電圧を加えた。これにより、始状態と終状態における磁化の熱揺らぎが抑制され、書き込みエラー率を大幅に改善できることが分かった。

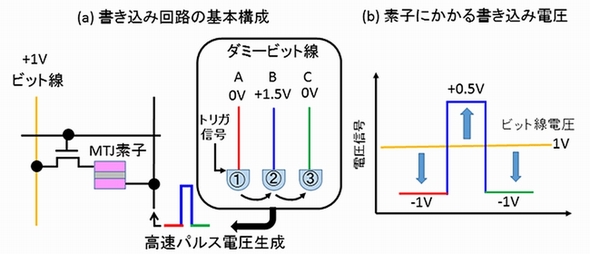

ところが、これらの効果を得るためには、パルス幅が1ナノ秒で、数百ピコ秒で極性反転を行うパルス電圧を、メモリアレイ内の素子に印加する必要がある。研究開発チームは、極性反転を伴う高速パルス電圧を生成できる電圧トルクMRAM専用の書き込み回路も新たに開発した。

例えば、A、B、Cと3本のダミービット線に、3段階の電圧をあらかじめ印加しておき、書き込み命令(トリガー信号)によって所定の電圧を発生させる。ダミービット線から供給される電圧はループ構造となっており、A、B、Cの順番に生成された高速パルス電圧が素子に印加される仕組みとした。一例だが、Aに0V、Bに1.5V、Cに0Vを印加しておけば、1.5Vのパルス電圧を生成することができるという。逆側のビット線に1Vの電圧を印加しておくと、素子には「−1V、0.5V、−1V」の極性反転を伴う高速パルスを印加することができる。

さらに、メモリ回路の無駄な動作を省く機能も開発した。逆極性のパルス電圧を印加している間に、読み出し動作を同時に行う。初期状態の記録情報を読み出して、書き込む情報がない場合にはその作業をスキップする。書き込み情報があれば、作業後に記録情報を再度確認する。書き込み時にエラーが生じていれば再度書き込み行う「エラー訂正プロセス」を高速で実行することができる。これらのエラー率低減手法を組み合わせることで、「実用化の目標となる、エラー率10-10〜10-15を達成することが可能になる」という。

今回は、書き込みエラー率の低減に関する研究以外でも、開発成果を上げた。新たに開発した読み出し回路は、読み出し電圧に対してMTJ素子の抵抗が変化する現象を活用した。これによって、電圧トルクMRAM用の高抵抗MTJ素子でも、情報読み出しを容易に行うことができるという。直径が30nmのメモリ素子における実測データを基に、書き込み/読み出しエラー率が改善されることをCMOS回路シミュレーションで明らかにした。今後、電圧磁気異方性制御の効率を、現状の3倍程度に高めることができれば、1〜2Gビット級のプロセッサ用ラストレベルキャッシュに適用することができるという。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

パッチ式脳波センサー、脳の状態を簡便に測定

パッチ式脳波センサー、脳の状態を簡便に測定

大阪大学産業科学研究所の関谷研究室を中心とする医脳理工連携プロジェクトチームは2016年8月、手のひらサイズの「パッチ式脳波センサー」を開発した。冷却シートを額に貼る感覚で容易に装着でき、脳の状態をリアルタイムに可視化することができるという。 光格子時計を応用、高精度に標高差を測定

光格子時計を応用、高精度に標高差を測定

東京大学の香取秀俊教授らによる研究グループは、光格子時計を用い直線距離で約15km離れた2地点間の標高差を精度5cmで測定することに成功した。将来は、火山活動やプレート運動など、地殻変動(標高変化)を精密に監視することも可能になるという。 多結晶並みの生産性で単結晶シリコン作製に成功

多結晶並みの生産性で単結晶シリコン作製に成功

科学技術振興機構(JST)は、多結晶シリコンインゴットに用いられるキャスト成長炉で、結晶性に優れる単結晶シリコンインゴットを作製する製造法を開発したと発表した。新製造法によるシリコンウエハーで、従来の単結晶シリコンと同等の変換効率で太陽電池を実現できることも確認したとする。 「縮環チオフェン」を簡便かつ短工程で合成

「縮環チオフェン」を簡便かつ短工程で合成

名古屋大学の伊丹健一郎教授らによる研究グループは、有機半導体に欠かせない分子群である「縮環チオフェン」を簡便に、かつ短い工程で合成できる新反応を開発した。 共有結合性有機ナノチューブ、簡便な合成法開発

共有結合性有機ナノチューブ、簡便な合成法開発

名古屋大学の伊丹健一郎教授らによる研究グループは、カーボンナノチューブに類似した筒状の新しい有機ナノチューブを簡便に合成する方法を開発した。 従来比10億分の1で動く分子センサー、単位はpJ

従来比10億分の1で動く分子センサー、単位はpJ

九州大学の柳田剛教授らの研究グループは、従来の10億分の1のエネルギーで駆動する分子センサーの開発に成功した。化学物質をモバイル端末で検知するといった応用が期待されるという。