ニュース

バンプレスTSV配線、熱抵抗は従来の3分の1:3〜4倍のDRAM積層を可能に(2/2 ページ)

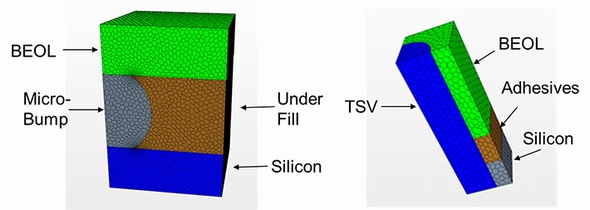

東京工業大学は、バンプレスTSV配線技術を用いると、3次元積層デバイスの熱抵抗を従来のバンプ接合構造に比べて3分の1にできることを明らかにした。メモリチップに適用すると、より多くのチップを積層することが可能となり、大容量化を加速する。

垂直接合部の熱抵抗は150分の1に

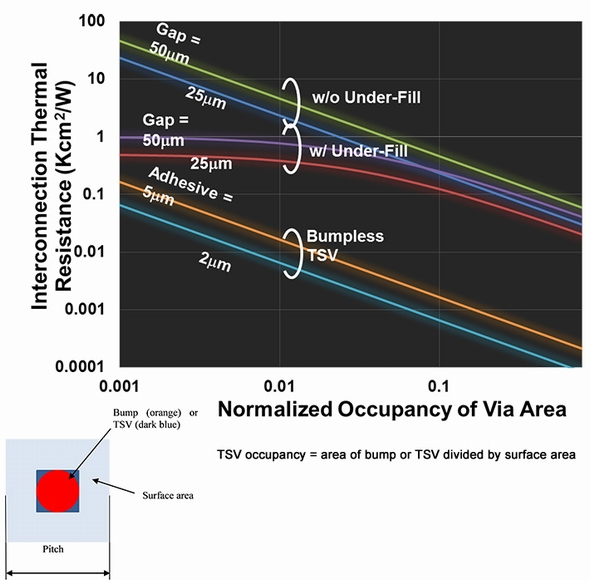

次に、マイクロバンプタイプとバンプレスタイプのFEMモデルを用いて、等価熱伝導率を求めた。この結果、バンプレスタイプにおける垂直接合部の熱抵抗は、マイクロバンプタイプに比べて、同じ占有率であれば150分の1に小さくなると推定した。

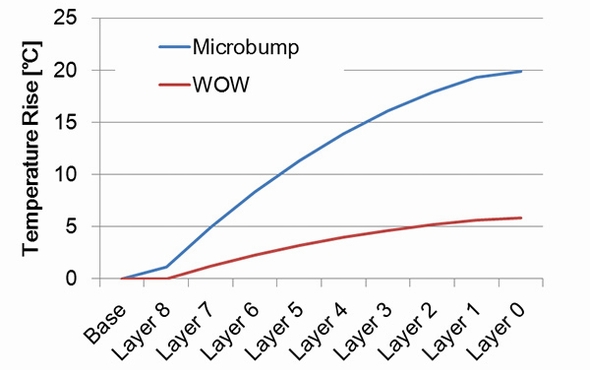

これらの解析結果から、バンプレスのTSV密度を全体の1%程度まで減らしても、熱抵抗を改善できることが分かった。また、各要素の熱抵抗から、全体の熱抵抗を算出した。従来のマイクロバンプタイプだと1.54Kcm2/Wに達した熱抵抗が、バンプレスタイプでは0.46Kcm2/Wに低減できることが分かった。さらに、それぞれの温度上昇分を推定したところ、マイクロバンプタイプでは温度が約20℃も上昇した。バンプレスタイプでは約4℃の上昇のとどまることが分かったという。

開発したバンプレスTSV配線技術を3次元DRAMに適用した場合、現行の温度上昇分を許容すると、現在より3〜4倍のDRAMチップを積層することが可能になるという。研究グループは今後、極めて薄いウエハーを積層し高密度TSV配線を行ったチップで実証実験を行い、携帯端末やサーバ向け大容量メモリ技術として実用化を急ぐ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

東工大ら、スピン電荷分離現象を直接観察

東工大ら、スピン電荷分離現象を直接観察

東京工業大学(東工大)らの共同研究グループは、時間軸で電荷信号とスピン信号の両波形を計測できる「スピン分解オシロスコープ」を実現した。これを用い、「朝永−ラッティンジャー液体」におけるスピン電荷分離現象を初めて直接観察した。 硬い透明セラミックス、シリコンと窒素から合成

硬い透明セラミックス、シリコンと窒素から合成

東京工業大学は、シリコンと窒素の原子が結合した化合物から、硬い透明セラミックスを合成することに成功した。開発した物質は全物質中で3番目の硬さを持ち、耐熱性はダイヤモンドを上回る。 東工大ら、パワーデバイス内部の電界を直接計測

東工大ら、パワーデバイス内部の電界を直接計測

東京工業大学の岩崎孝之助教らによる研究グループは、新たな電界センサーを開発し、パワーデバイス内部の電界を直接計測することに成功した。 有機ELの電子注入層と輸送層に向けた新物質

有機ELの電子注入層と輸送層に向けた新物質

東京工業大学の細野秀雄教授らは、有機ELディスプレイの電子注入層と輸送層に用いる透明酸化物半導体を開発した。新物質は従来の材料に比べて、同等の仕事関数と3桁以上も大きい移動度を持つ。 n型強磁性半導体を作製、伝導帯にスピン分裂

n型強磁性半導体を作製、伝導帯にスピン分裂

東京大学のレ デゥック アイン助教らは、強磁性半導体において大きなスピン分裂をもつ電子のエネルギー状態を初めて観測した。スピン自由度を用いた次世代半導体デバイスの実現に大きく近づいた。 室温で発光、円偏光スピンLEDの試作に成功

室温で発光、円偏光スピンLEDの試作に成功

東京工業大学の西沢望特任助教らは、室温で発光する円偏光スピンLEDの試作に成功した。ガン細胞の検出や暗号通信などへの応用が期待される。