連載

新材料「二酸化ハフニウム」を使った強誘電体キャパシターの特性:福田昭のストレージ通信(72) 強誘電体メモリの再発見(16)(2/2 ページ)

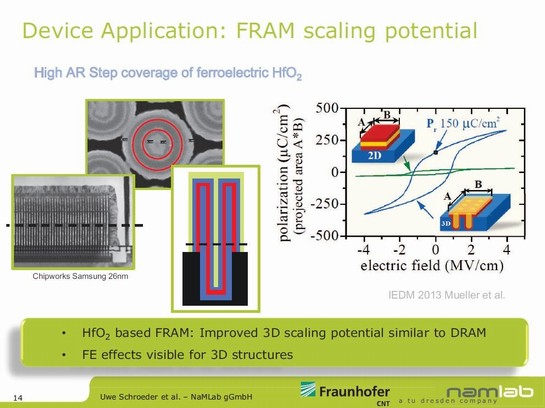

強誘電体の二酸化ハフニウムは、不揮発性メモリ用のキャパシターとしてどのような特性を示しているのか。後編となる今回は、分極反転サイクル特性と、シリコン面積当たりの静電容量を高めるための3次元構造について解説する。

高密度化の行方を左右する3次元構造の強誘電体キャパシター

DRAMセルの高誘電体キャパシターは、シリコン面積当たりの静電容量を高めるために、3次元構造を採用している。メモリセルの断面構造で説明すると、セル選択トランジスタの上、あるいは斜め上に円筒状のキャパシターを形成したり、シリコン基板に深い孔を開けて円筒状のキャパシターを形成したりする。

強誘電体不揮発性メモリ(FeRAM)でも、研究開発段階で同様の試みがなされたことがある。しかし従来のペロブスカイト系材料では、深い円筒状の薄膜における結晶品質があまり良好ではなく、3次元構造のキャパシターでは製品化には至らなかった。

新材料の二酸化ハフニウムでは幸いなことに、研究室レベルでは円筒状のキャパシターアレイで比較的良好な特性(ヒステリシス曲線)の強誘電体キャパシターが得られている。今後の研究開発の進展に、期待がかかる。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

SanDiskが語る、半導体不揮発性メモリの開発史

SanDiskが語る、半導体不揮発性メモリの開発史

今回からは、国際学会で語られたSanDiskの抵抗変化メモリ(ReRAM)の研究開発動向について紹介していく。まずは、約60年に及ぶ「不揮発性メモリの歴史」を振り返る。 モバイル機器のフラッシュストレージ

モバイル機器のフラッシュストレージ

2016年5月にパリで開催されたばかりの「国際メモリワークショップ(IMW:International Memory Workshop)」から、Micron Technologyが解説したメモリシステムについて紹介する。 電圧トルクMRAM、書き込みエラー率を低減

電圧トルクMRAM、書き込みエラー率を低減

産業技術総合研究所(産総研)は、電圧書込み方式磁気メモリ(電圧トルクMRAM)の書込みエラー率を従来の200分の1に低減する技術を開発した。 2017Q2のDRAM世界売上高、過去最高の165億ドルに

2017Q2のDRAM世界売上高、過去最高の165億ドルに

2017年第2四半期(4〜6月期)のDRAM世界売上高が、過去最高の165億米ドル以上となった。DRAMeXchangeの予測によると、DRAMの販売価格は2017年の残りの期間、引き続き上昇し続けるという。 2.5D(2.5次元)の新世代パッケージング技術

2.5D(2.5次元)の新世代パッケージング技術

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。 1ピコ秒の電場印加、絶縁体が金属へ瞬時に移転

1ピコ秒の電場印加、絶縁体が金属へ瞬時に移転

東京大学の岡本博教授らによる研究グループは、有機分子性結晶にテラヘルツパルス光を1ピコ秒間照射すると、絶縁体から金属へと瞬時に移転することを発見した。