IEDM 2017の講演2日目(12月5日)午後(その2):次世代トランジスタを狙う負性容量FET技術:福田昭のデバイス通信(122) 12月開催予定のIEDM 2017をプレビュー(6)(2/2 ページ)

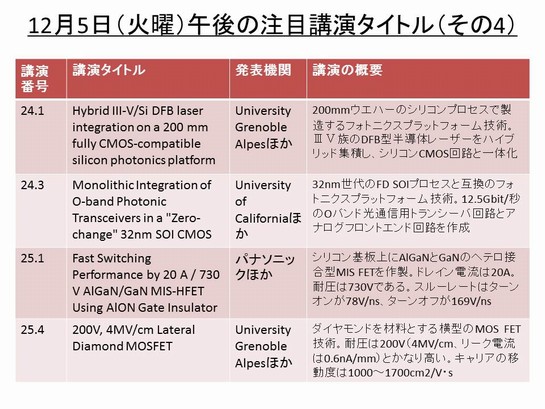

12月5日午後の注目講演を紹介する。負性容量トランジスタ、シリコンフォトニクス、非シリコン材料による高耐圧パワーデバイスなどの研究成果が発表される。

200mmのウエハープロセスでフォトニクス回路を製造

セッション24では、シリコン基板に光回路を作り込む、シリコンフォトニクスの研究報告が相次ぐ。最近は直径200mmのシリコンウエハープロセスでシリコンフォトニクス回路を製造するインフラが整っており、以前に比べるとはるかに低いコストで量産が可能になってきた。

University Grenoble AlpesとSTMicroelectronicsの共同研究チームは、200mmウエハーのシリコンプロセスで製造するフォトニクスプラットフォーム技術を発表する(講演番号24.1)。III-V族の分布帰還(DFB:Distributed FeedBack)型半導体レーザーをハイブリッド集積し、シリコンのCMOS回路と一体化する。半導体レーザーのサイドモード抑圧比(SMSR:Side Mode Suppression Ratio)は50dB。光導波路への出力は4mWである。

University of CaliforniaとMassachusetts Institute of Technology(MIT)の共同研究チームは32nm世代のFD SOI(完全空乏型シリコン・オン・インシュレーター)プロセスと互換のフォトニクスプラットフォーム技術を公表する(講演番号24.3)。12.5Gビット/秒のデータ転送速度で信号を送受信するO(Original)バンドの光通信用トランシーバー回路とアナログフロントエンド回路を集積してみせた。

窒化ガリウムのトランジスタで750Vの耐圧を達成

セッション25では、非シリコン材料による高耐圧パワーデバイスの研究成果が目立つ。窒化ガリウム(GaN)化合物半導体のトランジスタとダイヤモンドのトランジスタが登場する。

パナソニックと大阪大学、北海道大学の共同研究チームは、シリコン基板上に窒化アルミニウムガリウム(AlGaN)と窒化ガリウム(GaN)のヘテロ接合型MIS FETを作製した(講演番号25.1)。ドレイン電流は20A。耐圧は730Vである。スルーレートはターンオンが78V/ns、ターンオフが169V/nsと高い。

University Grenoble Alpesを中心とする共同研究グループは、ダイヤモンドを材料とする横型のMOSFET技術を発表する(講演番号25.4)。耐圧は200V(4MV/cm、リーク電流は0.6nA/mm)とかなり高い。キャリアの移動度は1000〜1700cm2/V・sに達する。

(次回に続く)

⇒「福田昭のデバイス通信」バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

IEDM 2017の技術講演初日、高密度ReRAMと紙基板の2次元トランジスタ

IEDM 2017の技術講演初日、高密度ReRAMと紙基板の2次元トランジスタ

技術講演初日である2017年12月4日から、注目の講演を紹介する。抵抗変化メモリ(ReRAM)や、折り曲げ可能な電子回路(フレキシブルエレクトロニクス)関連で、興味深い講演が多い。 IEDM 2017の全体スケジュールと基調講演

IEDM 2017の全体スケジュールと基調講演

ことしも「IEDM」の季節がやってきた。最先端電子デバイスの研究開発に関する国際学会「IEDM 2017」が、12月に米国で開催される。本シリーズでは、概要と注目の技術講演を紹介していく。 TSMC、7nm/EUVの開発状況をアップデート

TSMC、7nm/EUVの開発状況をアップデート

TSMCは2017年9月、米国で開催されたイベントで7nmプロセス技術やEUV(極端紫外線)リソグラフィの開発状況などを説明した。 東芝、SiC-MOSFETの抵抗を下げる新プロセス開発

東芝、SiC-MOSFETの抵抗を下げる新プロセス開発

東芝は2017年9月19日、SiC-MOSFETのチャネル領域の抵抗を約40%低減する新しいプロセス技術を開発したと発表した。 EUVの量産適用、半導体業界は前向きな見方

EUVの量産適用、半導体業界は前向きな見方

業界団体eBeam Initiativeの調査によると、EUV(極端紫外線)リソグラフィの実用化に対する業界の見方は、だいぶ前向きになっているようだ。 Hot Chips 2017、チップ積層技術に注目集まる

Hot Chips 2017、チップ積層技術に注目集まる

米国カリフォルニア州クパチーノで2017年8月20〜22日に開催された「Hot Chips 2017(Host Chips 29)」では、パッケージング技術やインターコネクト技術などを含め、特に2.5D(2.5次元)のチップ積層技術に注目が集まった。