ニュース

半導体プロセスの微細化は利益につながるのか:米で専門家が議論(2/2 ページ)

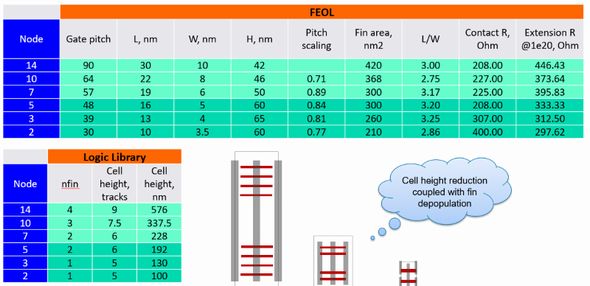

今後、半導体プロセスの微細化を進めていく上で、「微細化が本当に利益につながるのか」という疑問が出ているようだ。

“こなれていない”プロセス技術を使うファウンドリー

パネリストたちは、「成功への鍵は、ファウンドリーやEDA、設計エンジニアたちとの間で、強固な協業関係を構築することにある」との見解で合意している。Qualcommは、「こうした目標の実現に向けて、最適生産量を達成するためには、プロセス技術がもっと明確に定義された時点で、製造を開始する直前に最先端の設計技術を微調整する必要がある」と述べている。

Penzes氏は、「モバイルプロセッサ分野は非常に競争が激しく、競争力も高いため、ファウンドリー各社は、成熟度の低いプロセス技術を提供する傾向にある。だがこれを過度に利用すると平均単位原価が上昇し、競争力を失うことになる」と述べる。

同氏は、「新しいプロセス技術によってもたらされるはずの利益が、10%の変動によって全てが無になる可能性もある。このため、これまでは無意味な情報にすぎなかったようなことでも、やり残したままにしてはならない」と指摘する。

SynopsysのMoroz氏は、「金属配線の抵抗を低減するためのさまざまな技術を研究することで、さらなる高速化を実現できる可能性もある。複数のメタル層を接続するスーパービアなどの新しい構造だけでなく、コバルトやルテニウムなど新しい材料を使用することなどが挙げられる」と述べた。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Cadenceとimecが3nmチップを開発中、18年中にも完成

Cadenceとimecが3nmチップを開発中、18年中にも完成

imecとCadence Design Systemsが、3nmプロセスを適用したチップの開発を進めている。早ければ2018年後半にも開発が完了する見込みだとしている。 EUV、5nm付近でランダム欠陥 imecが報告

EUV、5nm付近でランダム欠陥 imecが報告

EUV(極端紫外線)リソグラフィの5nmプロセスで、ランダム欠陥が発生することを、imecの研究者が報告した。 微細化の減速、補うには新アーキテクチャに期待

微細化の減速、補うには新アーキテクチャに期待

「DesignCon 2018」で、IntelやArm、AMDの幹部らが、半導体プロセスの微細化などをテーマにパネルディスカッションを行った。微細化のスピードの減速を補うには、新しいコンピュータ/メモリアーキテクチャに期待したいと述べる。 ArmのAI戦略、見え始めたシナリオ

ArmのAI戦略、見え始めたシナリオ

機械学習についてなかなか動きを見せなかったArmだが、モバイルやエッジデバイスで機械学習を利用する機運が高まっているという背景を受け、少しずつ戦略のシナリオを見せ始めている。 “アナログ技術大国”へと変貌する中国

“アナログ技術大国”へと変貌する中国

中国の最新製品には、「欧米製チップ+中国製チップ」の組み合わせが非常に多くなっている。こうした新製品を分解して痛切に感じるのは、中国半導体メーカーが、“アナログ技術大国”になりつつある、ということだ。 EUVの量産適用、半導体業界は前向きな見方

EUVの量産適用、半導体業界は前向きな見方

業界団体eBeam Initiativeの調査によると、EUV(極端紫外線)リソグラフィの実用化に対する業界の見方は、だいぶ前向きになっているようだ。