ニュース

ポスト京は高密度がカギ、富士通が試作チップを公開:1チップに48計算コアを集積(2/2 ページ)

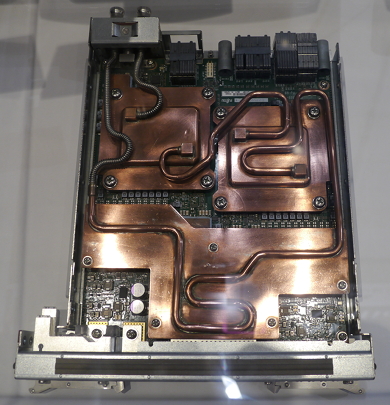

富士通は、同社のプライベートイベント「富士通フォーラム2018 東京」(2018年5月17〜18日、東京国際フォーラム)で、ポスト「京」スーパーコンピュータ(スパコン)に搭載される予定の「CPUパッケージ」とCPUパッケージを搭載した「CPUメモリユニット」の試作機を公開した。

コア数の異なる2種類のCPUパッケージを開発

CPUパッケージは、プロセッサとメモリ、Tofuインターコネクトのコントローラーを集積。ポスト京では、1つのCPUパッケージが1つの計算ノードとして扱われ、CPUメモリユニットには2つの計算ノード(CPUパッケージ)が搭載されている。

また、CPUパッケージは2種類の仕様があり、1つ目の仕様「計算ノード」は、48個の計算コアとOSやI/Oを処理する用途で2個の「アシスタントコア」で構成。もう1つの仕様「IO&計算ノード」では、48個の計算コアと4アシスタントコアを装備する。冷却方式は水冷を採用した。

同社担当者は、ポスト京の特長について「(プロセッサとメモリを同一パッケージに収める)CPUパッケージを採用することで、プロセッサとメモリを近接させメモリバンド幅の向上を狙っている」と語る。ポスト京よりArmアーキテクチャに変更した理由については「SPARCとLinuxの組み合わせより、ArmとLinuxの組み合わせの方が将来性がありエコシステムも発達しつつあるため」(同社担当者)とする。

また、現時点で具体的な性能などを話すことはできないと前置きしつつ、「技術者の思いとしては、世界で最も速いスーパーコンピュータとなることを目指して開発を進めている」(同社担当者)と抱負を語った。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ARMの新ベクトル命令「SVE」、ポスト京に採用へ

ARMの新ベクトル命令「SVE」、ポスト京に採用へ

米国で開催された「Hot Chips 28」において、ARMが新しいベクトル命令「SVE(Scalable Vector Extensions)」を発表した。富士通が、2020年を目標に開発しているポスト「京」スーパーコンピュータに採用されることが決まっている。 ArmのAI戦略、見え始めたシナリオ

ArmのAI戦略、見え始めたシナリオ

機械学習についてなかなか動きを見せなかったArmだが、モバイルやエッジデバイスで機械学習を利用する機運が高まっているという背景を受け、少しずつ戦略のシナリオを見せ始めている。 Intelの元社長、サーバ向けArm SoCで再始動

Intelの元社長、サーバ向けArm SoCで再始動

2015年にIntelを退任した、元プレジデントのRenee James氏が、Ampere ComputingのCEOとして、データセンター向けサーバ向けArm SoC(System on Chip)を発表した。データセンター向けサーバ市場は現在、Intelの独占状態だ。 Qualcomm、サーバ用ARM SoCを発表

Qualcomm、サーバ用ARM SoCを発表

Qualcommが、サーバ向けARM SoC(System on Chip)「Centriq」シリーズを発表した。「Centriq 2460」については、Intel「Xeon Platinum 8180」の競合品と位置付けている。 気象庁新型スパコンを日立が構築、18PFLOPSを達成

気象庁新型スパコンを日立が構築、18PFLOPSを達成

日立製作所は2018年5月16日、気象庁に新スーパーコンピュータ(スパコン)システムを納入し、同年6月5日から稼働を開始すると発表した。同システムは、浮動小数点演算において理論上ピーク性能が約18PFLOPS(従来システム比約21倍)に達し、気象庁で用いられている数値予報プログラムを約10倍の速度で実行できるという。 スパコン並みの脳機能コンピュータ、2030年に野球ボールサイズで実現へ

スパコン並みの脳機能コンピュータ、2030年に野球ボールサイズで実現へ

野球ボールサイズのてまり型スパコンが2030年に登場するのか。電子回路LSIの限界を超えるための技術として、シリコンフォトニクス技術が注目されている。新エネルギー・産業技術総合開発機構(NEDO)は「光エレクトロニクスシンポジウム」で、その可能性の一端を紹介した。