量産に向けた「EUV」の導入、最終段階へ:Samsungは2018年内にも適用開始(2/2 ページ)

次世代のリソグラフィ技術を立ち上げようとする20年に及ぶ努力が、最終段階に入った。EUV(極端紫外線)ステッパーを量産向けに導入することについて、複雑な課題があるにもかかわらず、専門家らは楽観的な見方を維持している。

imecはLERの低減とランダムエラーの排除に注力

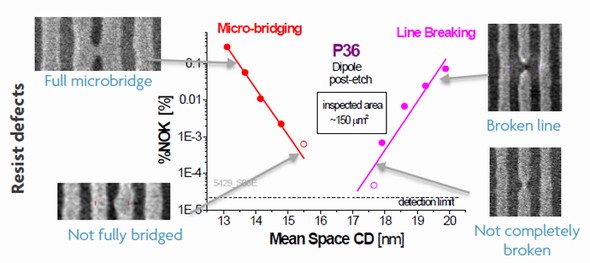

現在imecは、プロセス技術について2つの領域に注力している。LER(Line Edge Roughness)の低減と、ランダムエラーの排除である。

Steegen氏は、「“ハイブリッドソリューション”の適用が期待される」と述べている。つまり、スキャナーの設定やレジスト材料の選択、後工程の技術を組み合わせることで、欠陥修復を図れるとみている。

より照射量の高いEUV光(例えば、80mJ/cm2)を適用して、プロセスウィンドウ(製造条件の最適範囲)を広げることも可能だが、この手法ではスループットが低下する。Steegen氏は、「最初の実装におけるピーク照射量の決定は、ファウンドリーの判断にかかっている」と述べている。

一方、imecは、ランダムエラーが設計のどの時点で発生するのかを予測してマッピングすることで、プロセスウィンドウを規定している。欠陥の発見には通常、高速電子ビーム検査システムが多用される。

プロセスノードが一桁(10nm未満)に近づくと共に、研究者はエラーを、より詳細に分析するようになっている。例えば、EUV照射における光子の数は、化学増幅型レジストに影響する。その他のレジストの性能は、レジストが含む金属分子の構造によって変化する、といった具合だ。Steegen氏は、「レジストの研究はまだ基本段階にある」と述べている。

EUVへの移行を容易にするために、GLOBALFOUNDRIESは比較的安定している7nmを適用して、5つのメタル層でEUVを段階的に調整している。同社のCTO(最高技術責任者)を務めるGary Patton氏は、EE Timesのインタビューの中で、「より低い照射量で稼働すれば、スループットを上げられる」と語った。

GFは、AMD向けに7nmを

GLOBALFOUNDRIESは2018年後半に、液浸ステッパーを使用してAMDプロセッサ向けに初の7nmチップをテープアウトする計画である。さらに2019年には、IBM向けASICプロセッサを製造するという。

GLOBALFOUNDRIESの7nmチップとSRAMセルはTSMCの製品と類似していることから、AMDのような半導体設計企業は両方のファウンドリーを利用できるという。Patton氏は、「AMDには当社の製造能力を超える需要があるため、同社がTSMCを利用することに問題はない」と語った。

GLOBALFOUNDRIESは、「5nmノードはわずかな増分利得しか期待できないと考えられるため、10nmノードと同様に5nmノードをスキップする計画だ」としている。同社は3nmノードの開発に向け、資金面および技術面の両方でパートナーを探しているという。

さまざまな課題に直面しているにもかかわらず、Patton氏は今後の展望に前向きな見方を示している。スマートフォンが低迷する一方で、AI(人工知能)の活用が広がるにつれ、ファブレス半導体企業は新たな大規模市場を見いだした。Patton氏によると、GLOBALFOUNDRIESのFD-SOI(完全空乏型シリコン・オン・インシュレータ)は、2018年末までに75社の設計パートナーと36のデザインウィンを獲得する見通しだという。

【翻訳:青山麻由子、滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

堅調なTSMC、5nmのリスク生産は19年Q1にも開始

堅調なTSMC、5nmのリスク生産は19年Q1にも開始

TSMCは、半導体メーカーのファブライト化や、HPC(High Performance Computing)向けチップの需要の高まりにより、堅調な成長を続けている。7nmや5nmプロセスの開発も順調だとする。 SiCインゴットのスライス加工、完全自動化へ

SiCインゴットのスライス加工、完全自動化へ

ディスコは、「SEMICON Japan 2017」で、KABRAプロセスによるSiCインゴッドスライス工程を全自動化した装置などを実機展示した。 Infineon、300mm対応パワー半導体新工場を建設へ

Infineon、300mm対応パワー半導体新工場を建設へ

Infineon Technologiesは2018年5月18日、拡大の一途にあるパワー半導体の需要に対応すべく、今後6年間で約16億ユーロ(約18億8000万米ドル)を投じ、6万m△△2△△規模の新しい工場を設立すると発表した。 Samsung、3nm「GAA FET」の量産を2021年内に開始か

Samsung、3nm「GAA FET」の量産を2021年内に開始か

Samsung Electronicsは、米国カリフォルニア州サンタクララで2018年5月22日(現地時間)に開催したファウンドリー技術の年次フォーラムで、FinFETの後継アーキテクチャとされるGAA(Gate All Around)トランジスタを2021年に3nmノードで量産する計画を発表した。 TSMCがロードマップを発表、EUV導入は19年前半

TSMCがロードマップを発表、EUV導入は19年前半

TSMCは、7nmプロセスの量産を開始し、さらにEUV(極端紫外線)リソグラフィを導入したバージョンの生産を2019年前半にも開始する計画も発表した。さらに、同社は5nmノードに関する計画も明らかにした。 半導体プロセスの微細化は利益につながるのか

半導体プロセスの微細化は利益につながるのか

今後、半導体プロセスの微細化を進めていく上で、「微細化が本当に利益につながるのか」という疑問が出ているようだ。