ニュース

「ポスト京」の試作CPUが完成、機能試験を開始:2021年頃の共用開始を目指す

富士通と理化学研究所は2018年6月21日、ポスト「京」スーパーコンピュータ(スパコン)に搭載するCPUの試作チップが完成し、機能試験を開始したと発表した。

富士通と理化学研究所は2018年6月21日、ポスト「京」スーパーコンピュータ(スパコン)に搭載するCPUの試作チップが完成したと発表した。試作チップの初期動作確認が完了し、本格的な機能試験のフェーズに入る。

1CPU/1ノード構成のポスト京、48計算コアを1CPUに集積

ポスト京は、2021年頃の運用開始を目標に開発が進むスパコン。理化学研究所で現在運用中のスパコン「京」の後継機とされており、京の最大100倍となるアプリケーション実行性能を達成しつつ、消費電力を京の約3倍となる30〜40MW程度に収めることを目標としている。

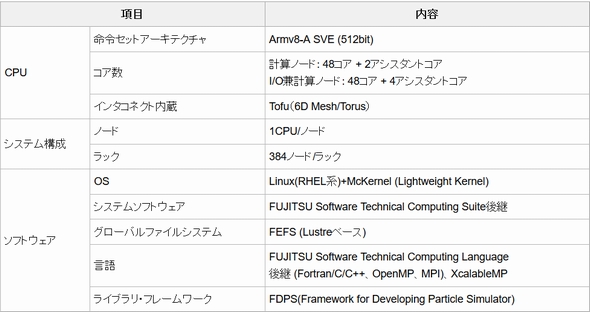

ポスト京のCPUは、命令セットアーキテクチャにFP16(16ビット浮動小数点)対応のArmv8-A、SIMD拡張命令セットにArmと富士通が共同開発したSVE(Scalable Vector Extensions)を採用。京で採用していたSPARCから切り替えている。これにより、「オープンソースソフトウェアなどを含めたソフトウェア資産が広く利用」できるとしつつも、京で蓄積したプログラム資産は「リコンパイルすることで確実な移行と性能確保」を行うという。

このCPUは48計算コアを集積し、1ノードに1CPUが搭載される。1ラックあたりのノード数は384。インターコネクトには、京で開発された6次元メッシュトーラス構成の「Tofu」に改良を加えたものを引き続き採用する。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ポスト京は高密度がカギ、富士通が試作チップを公開

ポスト京は高密度がカギ、富士通が試作チップを公開

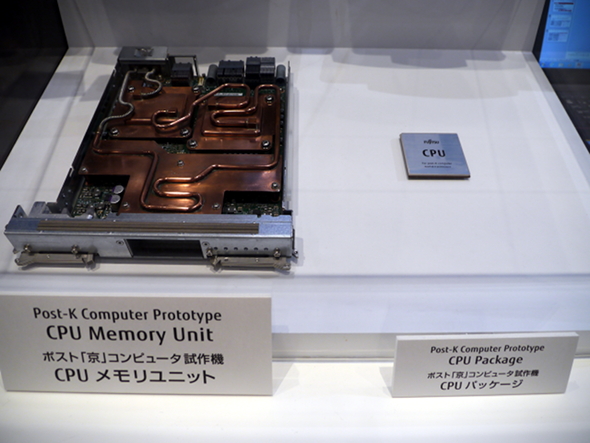

富士通は、同社のプライベートイベント「富士通フォーラム2018 東京」(2018年5月17〜18日、東京国際フォーラム)で、ポスト「京」スーパーコンピュータ(スパコン)に搭載される予定の「CPUパッケージ」とCPUパッケージを搭載した「CPUメモリユニット」の試作機を公開した。 ARMの新ベクトル命令「SVE」、ポスト京に採用へ

ARMの新ベクトル命令「SVE」、ポスト京に採用へ

米国で開催された「Hot Chips 28」において、ARMが新しいベクトル命令「SVE(Scalable Vector Extensions)」を発表した。富士通が、2020年を目標に開発しているポスト「京」スーパーコンピュータに採用されることが決まっている。 富士通のAIプロセッサ、演算精度とμアーキに工夫

富士通のAIプロセッサ、演算精度とμアーキに工夫

富士通は、同社のプライベートイベント「富士通フォーラム2018 東京」(2018年5月17〜18日、東京国際フォーラム)で、ディープラーニング処理に特化したプロセッサ「DLU(Deep Learning Unit)」を展示した。競合となる既存のアクセラレーターと比較して、10倍の電力性能比を実現するとしている。 気象庁新型スパコンを日立が構築、18PFLOPSを達成

気象庁新型スパコンを日立が構築、18PFLOPSを達成

日立製作所は2018年5月16日、気象庁に新スーパーコンピュータ(スパコン)システムを納入し、同年6月5日から稼働を開始すると発表した。同システムは、浮動小数点演算において理論上ピーク性能が約18PFLOPS(従来システム比約21倍)に達し、気象庁で用いられている数値予報プログラムを約10倍の速度で実行できるという。 ArmのAI戦略、見え始めたシナリオ

ArmのAI戦略、見え始めたシナリオ

機械学習についてなかなか動きを見せなかったArmだが、モバイルやエッジデバイスで機械学習を利用する機運が高まっているという背景を受け、少しずつ戦略のシナリオを見せ始めている。 「Cortex-A76」でノートPC市場も狙う、Armの戦略

「Cortex-A76」でノートPC市場も狙う、Armの戦略

Armは2018年5月31日(米国時間)、新しいモバイル向けCPUコア「Cortex-A76」を発表した。同社によると、Intelの最新「Core」プロセッサ(開発コード名:Skylake)の9割に相当する性能を実現できるという。