インドの新興企業、RISC-VベースのCPUコアを開発へ:Armへの対抗品となる?

インドの新興企業であるInCore Semiconductorsは、オープンソースの命令セットアーキテクチャ(ISA)である「RISC-V」ベースのプロセッサコアとディープラーニングアクセラレーター、SoC(System on Chip)設計ツールの設計とライセンス供与に関する意欲的な計画を発表した。

インドの新興企業であるInCore Semiconductorsは、オープンソースの命令セットアーキテクチャ(ISA)である「RISC-V」ベースのプロセッサコアとディープラーニングアクセラレーター、SoC(System on Chip)設計ツールの設計とライセンス供与に関する意欲的な計画を発表した。同社は、2018年末までに最初のコアを提供する計画だという。

同社の取り組みによって、規模は小さいながら重要な要素がRISC-Vエコシステムに加わることになる。つまり、InCore Semiconductorsの製品は、Armやその他の従来サプライヤーの製品に代わるものとして、世界的な関心を集めているのだ。

InCore Semiconductorsは、IIT-Madras(インド工科大学マドラス校)の「SHAKTI」プロセッサ研究チームからスピンアウトした企業で、ドイツのRobert Bosch AI(人工知能)センターで実施されている機械学習(マシンラーニング)の研究を活用している。InCore SemiconductorsのCEO(最高経営責任者)とIIT-Madrasの主任科学者を兼任するG. S. Madhusudan氏によると、同社はこれまでのところ、SHAKTIコアの商用サポートの提供による収益で資金を調達しているという。

InCore Semiconductorsは、超低消費電力のIoT(モノのインターネット)やデスクトップPCなどのエッジシステムを対象としたインオーダーのコアファミリーを2種類開発している。

ローエンドの「Eクラス」とハイエンドの「Cクラス」を用意

ローエンドの「Eクラス」コアは、3段パイプラインを使用し、RISC-V ISAのサブセットに対応した32ビットバージョンと64ビットバージョンを提供する。Armの「Cortex-M」クラスを狙ったもので、動作周波数は200MHz以下、FreeRTOSポートを備える。

ハイエンドの64ビット「Cクラス」コアは、5段パイプラインを使用し、フルセットのRISC-V ISAと仮想化に対応している。800MHzまでの動作周波数に対応しているが、最大2GHzにカスタマイズして、1サイクルあたり2つの命令を発行することができる。

Cクラスコアは、Linuxのセキュリティレベル「レベル4」に対応し、Armの「Cortex-A35」コアと「Cortex-A55」コアを意識したものとなっている。InCore Semiconductorsは、車載市場などに向けて耐障害性(フォールトトレランスト)機能を備えたCクラスコアの拡張セットのリリースも計画しているという。

EクラスコアとCクラスコアの両バージョンは、2018年末までにリリースする計画だとしている。スーパースカラーとデュアル発行の機能は、2019年4月までに利用可能になる見通しだという。

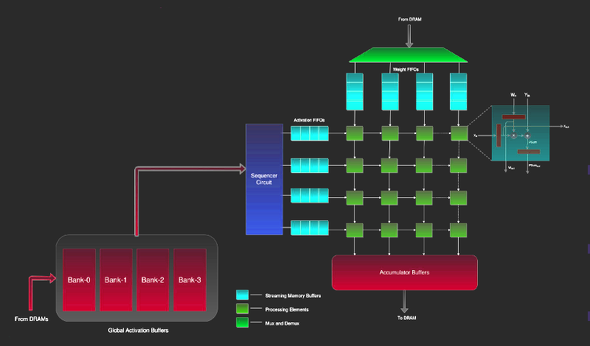

InCore Semiconductorsは、組み込みシステムのディープラーニングを加速させるために、2018年末までに同社のコアと統合するブロックを提供するとしている。これらのブロックは、機械学習向けアクセラレーターコアで、同社は「Axon」シリーズと名付けている。

1つのブロックは、データフローアーキテクチャを使用し、「Caffe」や「TensorFlow」などのディープラーニングフレームワークに対応した基本的なシストリックアレイを提供する。もう1つのブロックは、特殊なアドレステーブルとレジスタファイルを使用して、疎データセットの冗長操作をスキップできるようにするキャッシュを最適化する。

Madhusudan氏は、EE Timesとのメールのやりとりの中で、「われわれの製品は、どの工場でもテープアウトできる。7nmプロセスを適用することさえ可能だ」と述べている。「当社としては、IoTやサブギガヘルツクラスのデバイス向けには、Intelの22nmプロセスが適していると考えている」(同氏)

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「RISC-V」はEmbeddedでマーケットシェアを握れるのか

「RISC-V」はEmbeddedでマーケットシェアを握れるのか

2017年12月に開催された「RISC-V Day 2017 Tokyo」から、著者が注目した4つの講演を紹介する。 マイコンからHPCまで――RISC-Vが目指す“懐の深さ”

マイコンからHPCまで――RISC-Vが目指す“懐の深さ”

2017年12月18日に、「RISC-V Day 2017 Tokyo(リスクファイブの1日)」が開催され、RISC-V会長のKrste Asanović氏らがRISC-Vについて講演を行った。本記事では、基調講演を一部抜粋して紹介する。 関心高まるRISC-V、Armやx86の代替となり得るか

関心高まるRISC-V、Armやx86の代替となり得るか

2017年11月28〜30日にかけて、米国シリコンバレーで「7th RISC-V Workshop」が開催された。オープンな命令セットアーキテクチャ「RISC-V」は、Arm系やx86系の命令セットの代替となり得る技術として確実に台頭してきている。 RISC-Vベースチップ手掛ける新興企業が資金調達

RISC-Vベースチップ手掛ける新興企業が資金調達

RISC-VアーキテクチャをベースのCPUコアやカスタムSoCなどを手掛ける米国の新興企業SiFiveが合計1350万米ドルの資金を調達した。 Armの独壇場にはならない? AI向けコア市場

Armの独壇場にはならない? AI向けコア市場

CPUコアにおいて、多くの分野で高いシェアを誇るArmだが、AI(人工知能)エンジン向けチップのコアでは、独壇場とはいかないようだ。 Armが中国事業を合弁化、EUは中国に対し警笛

Armが中国事業を合弁化、EUは中国に対し警笛

ソフトバンクは2018年6月、Armの中国事業部門の全株式の51%を、中国投資企業およびエコシステムパートナーに7億7520万米ドルで売却することにより、中国国内でArmの事業を展開するための合弁企業を設立すると発表した。これを受けてEUは、中国の法律が欧州企業の知的所有権を侵害しているとして、世界貿易機関(WTO)において訴訟を起こした。