RISC-Vは大きな飛躍へ、エコシステムが拡大:各社から発表が相次ぐ(2/2 ページ)

「RISC-Vが、ビジネス向けに開放される」。RISC-Vの提唱者らは米国シリコンバレーで2018年12月4日に開催された、RISC-Vの第1回年次サミットにおいてこう主張した。

この1年でエコシステムが拡大

WDのCTO(最高技術責任者)を務めるMartin Fink氏は、「エコシステムは、ここ1年間で進化を遂げており、非常にうれしく思う。2017年には、Teslaなどの有名企業やツールベンダー数社が、メンバーとして参画した。次の段階として、TSMCやGLOBALFOUNDRIESなどのファウンドリー各社からも全面的な支持を得たいと考えている」と述べている。

注目はWDの発表

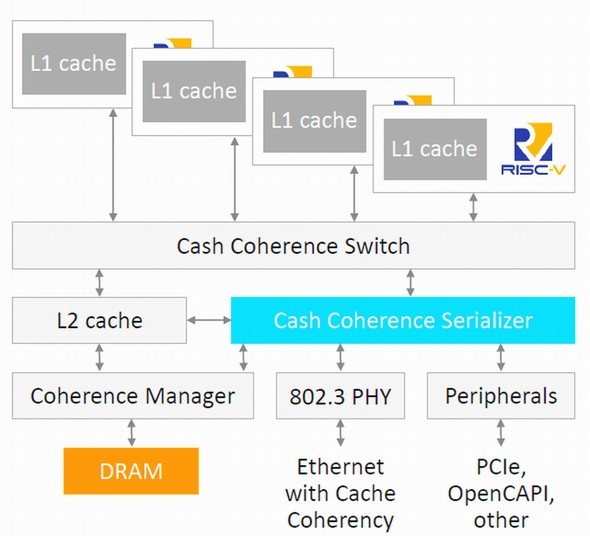

このイベントで最も驚いたことの1つは、RISC-Vプロセッサとアクセラレーター、メモリを接続したキャッシュコヒーレントなインターコネクト向けに開発したプロトコルをWDがオープンソースとして公開したことだ。WDのオープンネットワークプロトコル「OmniXtend」は、イーサネットの物理層(PHY)上でも動作できるので、増え続けるオープンなインターコネクトや特許インターコネクトの中で、RISC-Vの新たなポジションを確立すると期待される。

Fink氏は、「標準化団体CCIX Consortiumが策定するインターコネクト仕様『CCIX』とIBMのインターコネクト技術『OpenCAPI』は、どちらもファブリックプロトコルではなく、ポイント・ツー・ポイントプロトコルだ。Gen-Z Consortiumが策定するインターコネクト仕様『GenZ』はファブリックプロトコルだが、コヒーレンシのサポートは計画段階でまだ対応できていないので、イーサネットのような低コストのコモディティPHYには接続できない」と説明している。

WDはOmniXtendのコードをユーザーの希望に対応する形でリリースする予定だという。Fink氏は、「特定の企業だけが有利になることがないように設計する」と述べている。

同社は、顧客が望むあらゆるインタフェースに対応することを目指している。x86プロセッサだけに対応したIntelの独自インタフェース「Omni-Pat」やDDR-Tに代わる、オープンなインタフェースにしたい考えだ。

OmniXtendは2019年6月に、WDのプロトタイプボードとSiFiveのRISC-Vコア、米国の新興企業Barefoot Networksのイーサネットスイッチを使用して、実行コードをオープンソースの新言語「P4」で記述したシステムに実装する予定だという。WDは、設計対象の帯域幅やデータレートについては明らかにしていない。

WDはこれとは別に、32ビットのインオーダーコア「RISC-V SweRV Core」のオープンソースコードを2019年4月までにオンラインでリリースする予定だという。同コアは、28nmプロセスを適用。最大1.8GHzで動作し、4.91 CoreMarks/MHzの処理性能を実現する。性能スコアは、ArmやMIPSなどの多くのインオーダーコアやいくつかのアウトオブオーダーコアを上回るという。

Fink氏は、「当社初のRISC-Vコアは期待を上回る性能を実現したため、現在使用している他のコアに代わるコアになり得る」と述べている。

現在、SweRVコアのシミュレーター用のオープンソースコードを入手可能である。WDは、同コアをベースとした製品を2019年末にテープアウトする予定だという。

Fink氏がWDに入った2年前は、オープンソースは文化的規範ではなかった。そのため、SweRVコアとプロトコルの開発には反対の声が上がることも覚悟したが、WDの経営陣は開発チームを支援したという。「その結果、当社はオープンな強みを獲得することができた」とFink氏は述べている。

WDの最先端技術開発チームは、2014年にRISC-Vコアの開発を開始したという。Fink氏は、「開発チームから開発状況の報告を受ける中で、私はオープンソースモデルについての知識を深め、その素晴らしさを認識した。そしてついに、業界を変革するチャンスが訪れた」と語った。

【翻訳:滝本麻貴、田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「RISC-V」はEmbeddedでマーケットシェアを握れるのか

「RISC-V」はEmbeddedでマーケットシェアを握れるのか

2017年12月に開催された「RISC-V Day 2017 Tokyo」から、著者が注目した4つの講演を紹介する。 マイコンからHPCまで――RISC-Vが目指す“懐の深さ”

マイコンからHPCまで――RISC-Vが目指す“懐の深さ”

2017年12月18日に、「RISC-V Day 2017 Tokyo(リスクファイブの1日)」が開催され、RISC-V会長のKrste Asanović氏らがRISC-Vについて講演を行った。本記事では、基調講演を一部抜粋して紹介する。 インドの新興企業、RISC-VベースのCPUコアを開発へ

インドの新興企業、RISC-VベースのCPUコアを開発へ

インドの新興企業であるInCore Semiconductorsは、オープンソースの命令セットアーキテクチャ(ISA)である「RISC-V」ベースのプロセッサコアとディープラーニングアクセラレーター、SoC(System on Chip)設計ツールの設計とライセンス供与に関する意欲的な計画を発表した。 RISC-V、中国で勢力を拡大

RISC-V、中国で勢力を拡大

今回開催されたイベントに参加した2社のベンダーが発表したレポートによると、中国では現在、RISC-Vの勢いが拡大しているという。 データ中心を加速、WDがRISC-Vプロセッサ開発に本腰

データ中心を加速、WDがRISC-Vプロセッサ開発に本腰

Western Digital(ウエスタンデジタル/WD)は2018年6月21日、東京都内で記者会見を開催し、オープンソースのISA(命令セットアーキテクチャ)である「RISC-V」について、同社の取り組みを説明した。 関心高まるRISC-V、Armやx86の代替となり得るか

関心高まるRISC-V、Armやx86の代替となり得るか

2017年11月28〜30日にかけて、米国シリコンバレーで「7th RISC-V Workshop」が開催された。オープンな命令セットアーキテクチャ「RISC-V」は、Arm系やx86系の命令セットの代替となり得る技術として確実に台頭してきている。