半導体業界のトレンドは「3次元化」が明確に VLSI 2019:過去最高の出席者数で大盛況(4/4 ページ)

2019年のVLSIシンポジウム(以下、VLSI)が6月9〜14日に、京都のリーガロイヤルホテルで開催された。今後の半導体業界の進む方向性を伺える内容が多かったのでレポートする。

Technology Evening Panel Discussion

現在の半導体業界(特にデバイス・プロセス関係者)の集合意識が、6月11日(火)の夜に行われたTechnology Evening Panel Discussionで垣間見えた気がする。

テーマは“What Will the Foundries of the Future Do?(将来のファウンドリーは何をするのか)”で、東京エレクトロン(TEL)のAnton DeVilliers氏がモデレーターを務め、以下の6人がパネラーとして参加した。

- Kaizad Mistry氏:Intel VP of technology & manufacturing

- Anthony Yu氏:GLOBALFOUNDRIES VP of Si foundry

- Chidi Chidambaram氏:Qualcomm VP of Si tech/foundry

- Paul Jung氏:Samsung Electronics VP

- 大場隆之氏:東京工業大学 特任教授

- Kevin Zhang氏:TSMC VP of business development

このPanel Discussionでは、各パネラーが5〜10分程度のシュートプレゼンテーションを行った後、質問を提示し、会場の出席者がスマートフォンで回答を投票するというスタイルが取られた。

会場をざっと見たところ、150人程度の出席者がいた。その所属は、半導体メーカー、装置メーカー、材料メーカーと多様であるが、半導体業界の一つの“空気”が読み取れたように思う。以下に各質問と回答結果を示す。

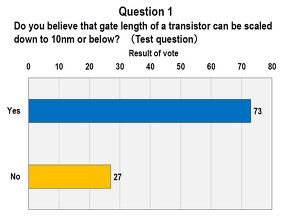

Q1 Do you believe that gate length of a transistor can be scaled down to 10nm or below? (Test question)(トランジスタのゲート長は、10nm以下まで微細化できると思いますか?【※テストのために設けられた質問】)

73人が“Yes”と回答し、27人が”No“と回答した。つまり、半導体業界人の多くが、ゲート長は10nm以降も微細化されると思っている訳だ。ちなみに筆者も、”Yes”に投票した。

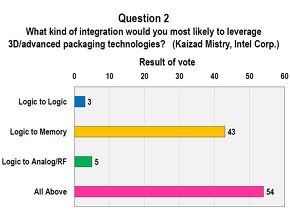

Q2 What kind of integration would you most likely to leverage 3D/advanced packaging technologies? (Kaizad Mistry, Intel)(どのようなチップの統合において、3D/最先端パッケージが活用されると思いますか?【IntelのKaizad Mistry氏による質問】)

筆者が今後の半導体技術のトレンドと捉えた3次元化について、半導体業界人の43人がロジックとメモリが積層されると回答し、何と54人が“All Above”と回答した。3次元化のトレンドは、どうやら本物であると考えられる。

Technology Evening Panel Discussionの質問と回答数 出典:VLSI symposium 2019 / Technology panel discussion(クリックで拡大)

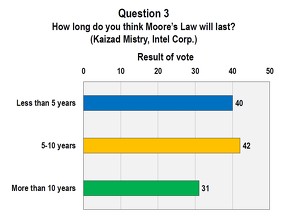

Technology Evening Panel Discussionの質問と回答数 出典:VLSI symposium 2019 / Technology panel discussion(クリックで拡大)Q3 How long do you think Moore’s Law will last?(Kaizad Mistry, Intel)(ムーアの法則は、あとどのくらい続くと思いますか?【同上】)?

この回答は3つに分かれた。ムーアの法則が5年以内に終わると回答した人が40人、5〜10年以内が42人、10年以上続くと回答した人が31人だった。ちなみに筆者は、10年以上に投票した。

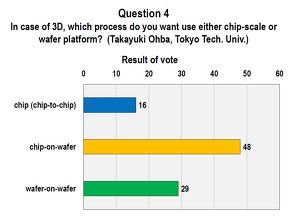

Q4 In case of 3D, which process do you want use either chip-scale or wafer platform?(Takayuki Ohba, Tokyo Tech. Univ.)(3Dにおいて、チップスケールあるいはウエハープラットフォームの、どちらのプロセスを使いたいですか?【東京工業大学 特任教授 大場隆之氏による質問】)

この質問への回答で最も多かったのが“Chip on Wafer”の48人だった。筆者は、29人が支持した”Wafer on Wafer”に一票を投じた。

Technology Evening Panel Discussionの質問と回答数 出典:VLSI symposium 2019 / Technology panel discussion(クリックで拡大)

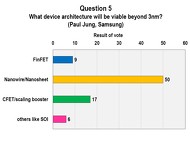

Technology Evening Panel Discussionの質問と回答数 出典:VLSI symposium 2019 / Technology panel discussion(クリックで拡大)Q5 What device architecture will be viable beyond 3nm?(Paul Jung, Samsung)(3nm以降では、どのようなデバイスアーキテクチャが用いられると思いますか?【Samsung Electronics Paul Jung氏による質問】)

最も多かった回答は、Nanowire/Nanosheetの50人だった。ちなみに筆者は、17人が投票したComplementary FET(CFET)/scaling boosterに一票を入れた。

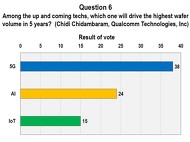

Q6 Among the up and coming techs, which one will drive the highest wafer volume in 5 years?(Chidi Chidambaram, Qualcomm Technologies, Inc)(新しい技術のうち、今後5年間で最もウエハー出荷量が多くなるものは何だと思いますか?【Qualcomm Technologies Chidi Chidambaram氏による質問】)

5G(第5世代移動通信)が38人、AIが24人、IoTが15人だった。“in 5 years”という制限つきだったため、このような回答になったと思われる。“in 10 years”だったら、例えばAIなど、違った結果が最多になったのではないか。

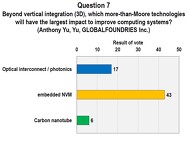

Q7 Beyond vertical integration (3D), which more-than-Moore technologies will have the largest impact to improve computing systems?(Anthony Yu, GLOBALFOUNDRIES Inc.)(3次元化以降について、どの“more than Moore”のテクノロジーが、コンピュータシステムの性能向上に最も大きな影響を与えると思いますか?【GLOBALFOUNDRIES Anthony Yu氏による質問】)

embedded NVM (Non Volatile Memory)が43人と最多で、次いでOptical interconnect/photonicsが17票を集めた。ちなみに筆者は、embedded NVMに投票した。

Technology Evening Panel Discussionの質問と回答数 出典:VLSI symposium 2019 / Technology panel discussion(クリックで拡大)

Technology Evening Panel Discussionの質問と回答数 出典:VLSI symposium 2019 / Technology panel discussion(クリックで拡大)以上がTechnology Evening Panel Discussionでの質問と回答である。何となく、半導体業界が進むであろう方向性が見えた気がした。モデレーターやパネリストだけでなく、出席者全員にとって、非常に良いマーケテイングになったのではないだろうか。読者諸賢の回答は、いかがであろうか?

筆者プロフィール

湯之上隆(ゆのがみ たかし)微細加工研究所 所長

1961年生まれ。静岡県出身。京都大学大学院(原子核工学専攻)を修了後、日立製作所入社。以降16年に渡り、中央研究所、半導体事業部、エルピーダメモリ(出向)、半導体先端テクノロジーズ(出向)にて半導体の微細加工技術開発に従事。2000年に京都大学より工学博士取得。現在、微細加工研究所の所長として、半導体・電機産業関係企業のコンサルタントおよびジャーナリストの仕事に従事。著書に『日本「半導体」敗戦』(光文社)、『「電機・半導体」大崩壊の教訓』(日本文芸社)、『日本型モノづくりの敗北 零戦・半導体・テレビ』(文春新書)。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

組み込みAIを加速する、ルネサスの新Processing-in-Memory

組み込みAIを加速する、ルネサスの新Processing-in-Memory

ルネサス エレクトロニクスは、メモリ回路内でメモリデータの読み出し中に積和演算を行う既存のProcessing-in-Memory(PIM)を改良した、新たなPIM技術を開発したと発表した。同技術をベースに開発したAIアクセラレーターをテストチップに実装して推論処理を行ったところ、8.8TOPS/Wの電力効率を実証したという。 ルネサス、SOTBプロセス用低電力フラッシュ技術

ルネサス、SOTBプロセス用低電力フラッシュ技術

ルネサス エレクトロニクスは、65nmのSOTB(Silicon On Thin Buried Oxide)プロセスに混載可能なフラッシュメモリの低消費電力化技術を開発した。 メモリ不況の夜明けは近い、市場動向から見たDRAMとNANDの挙動

メモリ不況の夜明けは近い、市場動向から見たDRAMとNANDの挙動

世界半導体市場統計(WSTS)のデータを用いて市場動向をグラフにしてみたところ、両者の挙動が大きく異なることを発見した。本稿では、その挙動を示すとともに、その理由を考察する。その上で、二つのメモリ市場の未来を展望する。 3D NANDフラッシュメモリの断面構造と製造工程

3D NANDフラッシュメモリの断面構造と製造工程

2018年5月に開催された国際会議「IMW」で行われたセミナー「3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望」の概要をシリーズで紹介している。今回は、3D NANDフラッシュメモリの断面構造と、メモリセルアレイの製造工程を解説しよう。 Intelが新しい3D積層チップ技術「Foveros」を発表

Intelが新しい3D積層チップ技術「Foveros」を発表

Intelは、新しい3Dパッケージング技術「Foveros」のデモを披露した。2019年後半には提供できる見込みだという。Intelは、このFoverosの開発に20年間を費やし、ロジックとメモリを組み合わせた3D(3次元)のヘテロジニアス構造でダイ積層を実現した。 3D NANDフラッシュ製造のカギとなるプロセス技術

3D NANDフラッシュ製造のカギとなるプロセス技術

今回は、3D NANDフラッシュメモリの製造プロセスにおける重要な技術(キープロセス)について解説する。