AIチップ設計拠点を公開、試験運用を開始:中小・ベンチャー企業を支援

新エネルギー・産業技術総合開発機構(NEDO)は、東京大学浅野キャンパス(東京都文京区)内に設けた「AIチップ設計拠点」の試用準備が整ったため、中小・ベンチャー企業を中心に拠点を公開し、試験運用を始めた。

遠隔地のサテライト拠点などからも利用可能

新エネルギー・産業技術総合開発機構(NEDO)は2019年10月、東京大学浅野キャンパス(東京都文京区)内に設けた「AIチップ設計拠点」の試用準備が整ったため、中小・ベンチャー企業を中心に拠点を公開し、試験運用を始めると発表した。

NEDOは、AIチップの開発を加速するために、イノベーション推進事業を展開している。この一環として、産業技術総合研究所(産総研)や東京大学と共同で、AIチップ設計の拠点整備を進めてきた。

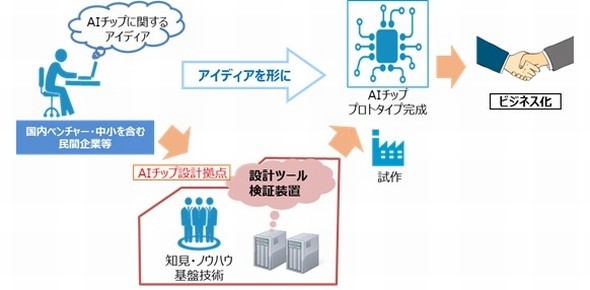

試験運用を始める設計拠点には、AIチップ設計に必要となるEDAツールやハードウェアエミュレーター、標準IPコアが用意されている。また、AIチップ設計に必要な共通基盤技術の開発、知見やノウハウの蓄積、人材育成などにも取り組む。これらの活動を通じて、中小・ベンチャー企業が保有するアイデアをチップに落とし込み、革新的な構想を具現化するための支援を行う。

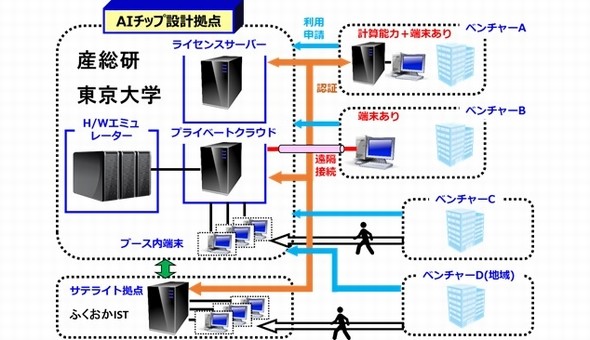

AIチップ設計拠点は、直接訪問して設計環境を利用することができるほか、遠隔地からもネットワークを介して利用することが可能だ。福岡県産業・科学技術振興財団(ふくおかIST)は、ロボット・システム開発センター(福岡システムLSI総合開発センター)内に地域サテライトを設けている。このブースからも本拠点の設計環境が利用できる。福岡以外でも、地域サテライト拠点を増やしていく予定である。

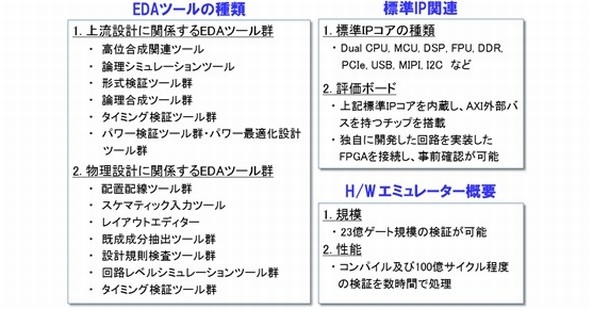

設計環境としては、上流設計や物理設計を行うためのEDAツール群を始め、23億ゲートの大規模回路で100億サイクルを数時間で検証できるハードウェアエミュレーター、28nm/40nmプロセスを利用できる標準インタフェース回路などの標準IPコアなどを用意した。これら標準IPコアを搭載した評価ボードを用いて、利用者が開発した回路との接続性などを事前に検証することもできる。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

産総研と東大、AI機能付きDASチップの開発加速

産総研と東大、AI機能付きDASチップの開発加速

産業技術総合研究所(産総研)エレクトロニクス・製造領域は、東京大学浅野キャンパス内に、「産総研・東大AI(人工知能)チップデザインオープンイノベーションラボラトリ」(AIDL)を、東京大学大規模集積システム設計教育研究センター(VDEC)と共同で設立した。 NEDOとOKI、深層学習モデルの軽量化技術を開発

NEDOとOKI、深層学習モデルの軽量化技術を開発

新エネルギー・産業技術総合開発機構(NEDO)と沖電気工業(OKI)は、ディープラーニング(深層学習)モデルの軽量化技術を開発した。 NEDOら、小型の16波長多重光回路チップを開発

NEDOら、小型の16波長多重光回路チップを開発

新エネルギー・産業技術総合開発機構(NEDO)と光電子融合基盤技術研究所(PETRA)は共同で、小型の16波長多重光回路チップを開発した。1波長当たり32Gビット/秒という高密度信号伝送での動作を確認した。 NEDOら、機能性材料の開発期間を短縮可能に

NEDOら、機能性材料の開発期間を短縮可能に

新エネルギー・産業技術総合開発機構(NEDO)と産業技術総合研究所、先端素材高速開発技術研究組合(ADMAT)は、革新的な機能性材料の開発を効率よく行うための「シミュレーター」を開発し、順次公開する。 NEDOら、オンボード光モジュールで400Gbps実現

NEDOら、オンボード光モジュールで400Gbps実現

新エネルギー・産業技術総合開発機構(NEDO)と光電子融合基盤技術研究所(PETRA)は、外形寸法が34×36×8mmと極めて小さいオンボード光モジュールを用いて、400Gビット/秒(bps)の伝送速度を実現した。 4波長多重光受信チップを5mm角以下で実現

4波長多重光受信チップを5mm角以下で実現

新エネルギー・産業技術総合開発機構(NEDO)と光電子融合基盤技術研究所(PETRA)、沖電気工業(OKI)は、40Gビット/秒の光信号に対応する超小型4波長多重光受信チップを開発し、受信動作を実証した。