実装設備が対応すべき部品と搭載精度のロードマップ:福田昭のデバイス通信(273) 2019年度版実装技術ロードマップ(81)

今回から、第6章「実装設備」の第4節「実装技術動向」を説明する。まずはチップ部品の技術ロードマップを取り上げる。

2028年までの技術ロードマップを作成

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」に関する完成報告会(2019年6月4日に東京で開催)と同ロードマップの概要をシリーズでご報告している。今回はその第81回である。

本シリーズの第3回から第22回までは第2章「注目される市場と電子機器群」の概要、第23回から第30回までは第3章「電子デバイスパッケージ」の概要、第31回から第63回までは第4章「電子部品」の概要、第64回から第72回までは第5章「プリント配線板」の概要を説明してきた。

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第73回から、第6章「実装設備」(プログラムの10番)の概要を紹介している。出典:JEITA(クリックで拡大)

第73回からは、第6章「実装設備」の内容を解説している。第76回から前回(第81回)までは、実装設備のユーザー(セットメーカーやモジュールメーカー、アセンブリ受託企業)が実装設備に要求する項目を、JEITAがアンケート調査した結果をご報告してきた。第6章の第3節に対応する部分だ。

今回からは第6章第4節に対応する部分の概要をご説明していく。タイトルは「実装技術動向」である。この節は第1項「部品対応力」、第2項「プリント配線板対応力」、第3項「部品供給方式への対応力」。第4項「接合材料」、第5項「封止材料」で構成される。今回は第1項「部品対応力」の概要を解説する。

チップ部品の最先端は「0201サイズ」が当面続く

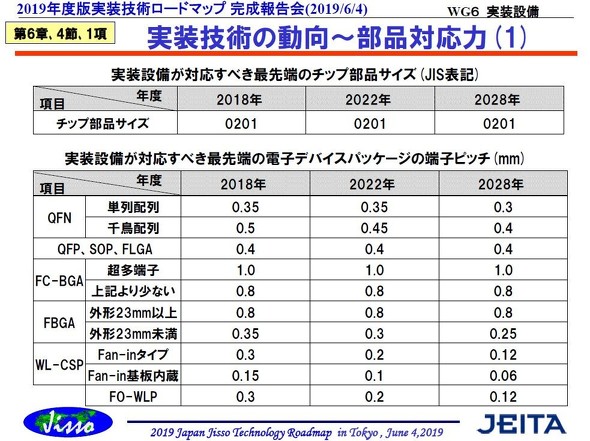

部品対応力とは、実装設備が対応すべき部品の大きさや端子ピッチなどを指す。始めはチップ部品を扱う。小型化が進んでいる分野だ。

前回版(2017年版 実装技術ロードマップ)では、2018年には0201部品(大きさが0.25mm×0.125mmのチップ部品)が量産品に採用されていくと予測した。しかし実際の採用は一部の電子機器にとどまっている。従って2018年〜2028年に実装設備が対応すべきチップ部品の最小サイズは「0201」で変わらないと予測した。

電子デバイスパッケージ(半導体パッケージ)の全体動向については第3章第3節(本シリーズの第24回)で説明した。多端子化と小型化、薄型化が各種のパッケージで進んでいる。ここでは半導体パッケージをQFN(リードレス)、QFP系(リード端子あり)、FC-BGA(超多端子用BGA)、FBGA、WL-CSP、FO-WLPに分けて端子ピッチのロードマップを掲載した。

端子ピッチが最も狭い(基板内蔵用を除く)のはWL-CSPとFO-WLPである。2018年の時点で0.3mmであり、10年後の2028年には0.12mmと短くなる。

高い搭載精度を要求するWL-CSPとFO-WLP

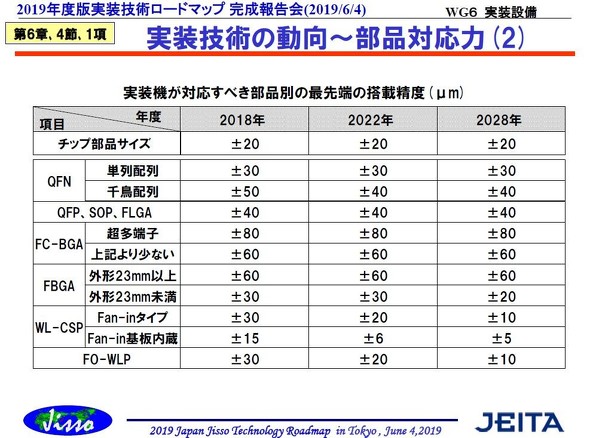

チップ部品と半導体パッケージの搭載精度に関しても、実装技術が達成すべき値をロードマップとして示した。ただし、ここで示すロードマップは部品と基板の寸法ばらつきを考慮していないので留意されたい。

搭載精度の目標値はおおよそ、端子ピッチの10分の1である。例えば端子ピッチが0.4mmのQFPが要求する搭載精度は±40μmとなる。既に述べたように端子ピッチが最も狭いパッケージはWL-CSPとFO-WLPである。搭載精度は2018年の時点で±30μmを要求する。2028年には±10μmと非常に高い精度が要望されるようになる。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ベアチップ/フリップチップを高い精度で装着

ベアチップ/フリップチップを高い精度で装着

実装設備に要求する項目のアンケート結果を紹介するシリーズ。今回は「ベアチップ/フリップチップボンダ」に対する要求を説明する。 重要さを増す検査機からのフィードバック

重要さを増す検査機からのフィードバック

引き続き、実装設備に要求する項目のアンケート結果を紹介する。今回は、「検査機」に対する要求と対策を取り上げる。 高速・高精度・低コストの実装工程を支える設備と材料

高速・高精度・低コストの実装工程を支える設備と材料

第6章「実装設備」の概要を説明する。まずは表面実装の設備と材料を取り上げる。 HDD大手SeagateとWDの2020会計年度業績、売り上げはいずれも約1%増に

HDD大手SeagateとWDの2020会計年度業績、売り上げはいずれも約1%増に

今回は、Seagate TechnologyとWestern Digital(WD)の2020会計年度の業績を紹介しよう。 HDD大手Western Digitalの業績、前期比の営業利益が4四半期連続で増加

HDD大手Western Digitalの業績、前期比の営業利益が4四半期連続で増加

今回は、Western Digital(WD)の2020会計年度第4四半期(2020年4月〜6月期)の業績を紹介する。 半導体パッケージ基板の技術ロードマップ

半導体パッケージ基板の技術ロードマップ

今回から、第3節「プリント配線板技術ロードマップ」の概要をお届けする。まずは「半導体パッケージ基板(サブストレート)」のロードマップを紹介する。