複数AIアクセラレーター搭載の評価チップを試作:AIチップの設計期間を半分以下に

新エネルギー・産業技術総合開発機構(NEDO)と産業技術総合研究所(産総研)および、東京大学は共同で、仕様が異なる6種類のAIアクセラレーターを搭載した評価チップ「AI-One」を設計、試作を始めた。これを活用すると、短い期間で安価にAIチップの設計と評価が可能になる。

28nmCMOSプロセスを用いて製造

新エネルギー・産業技術総合開発機構(NEDO)は2021年5月、産業技術総合研究所(産総研)や東京大学と共同で、仕様が異なる6種類のAIアクセラレーターを搭載した評価チップ「AI-One」を設計、試作を始めたと発表した。これを活用すると、短い期間で安価にAIチップの設計と評価が可能になるという。

NEDOはAIチップの開発を加速するため、産総研や東京大学と共同で、東京大学浅野キャンパス(東京都文京区)内の武田先端知ビルにAIチップ設計拠点を設け、半導体設計に必要となる共通基盤技術の開発やEDAツール、標準IPコアなどの整備を進めてきた。

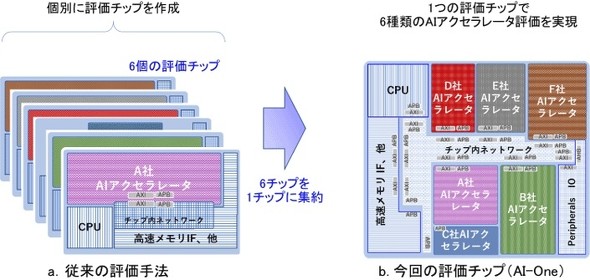

中小・ベンチャー企業などが開発する独自のAIアクセラレーター向け評価プラットフォームの構築もその1つである。共通基盤技術として標準システム回路や検証回路、テスト回路および、評価ボードなどを用意し、AIアクセラレーター向け評価プラットフォームとして提供する。これらを活用することで、各企業が開発したAIアクセラレーターを実環境で動作させ、評価することが可能になるという。

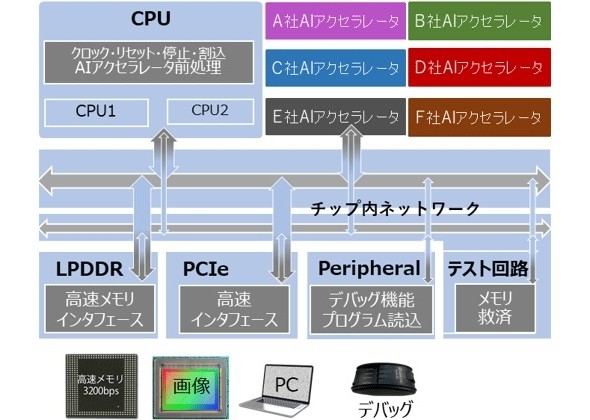

今回、仕様が異なる6種類のAIアクセラレーターを搭載した評価チップの設計を完了。外部のファウンドリに委託し、28nmCMOSプロセスを用いて試作を始めた。エッジAI向け評価プラットフォームには、複数のAIアクセラレーターやデュアルコア構成のCPU、チップ内ネットワーク、テスト回路および、LPDDRやPCIeといったインタフェースなどを集積している。

AIアクセラレーター開発者は、AIチップ設計拠点にある設計クラウド上で、各自が開発したAIアクセラレーターを評価プラットフォームに組み込めば、チップ実装時の動作周波数や消費電力、性能などを設計段階で見積もることが可能になる。これにより、AIチップの開発時間を、従来の45%以下に短縮できるという。複数のAIアクセラレーターを同一チップ上に集積し評価できるため、試作コストの低減にもつながるとみている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

産総研、仮想実験環境で材料の電気的特性を予測

産総研、仮想実験環境で材料の電気的特性を予測

産業技術総合研究所(産総研)は、第一原理計算シミュレーターとAI技術を連携させることで、実験データと同等の電気伝導度を計算する基盤技術を開発した。研究成果を用いると、材料の開発期間を大幅に短縮できる可能性がある。 東京大、高い伝導特性を有する導電性高分子を開発

東京大、高い伝導特性を有する導電性高分子を開発

東京大学らの研究グループは、従来に比べ高い結晶性と伝導特性を有する導電性高分子を開発した。これまでより酸化力が強いラジカル塩ドーパントを独自開発し、これを高分子半導体に作用させることで実現した。 ナノすりガラス、nm級凹凸加工で超親水性を実現

ナノすりガラス、nm級凹凸加工で超親水性を実現

東京大学らの研究グループは、ナノメートル級の凹凸を設けた「ナノすりガラス」を開発した。ナノすりガラスの表面は、150℃という高温でも長時間にわたって超親水性を維持することができ、有機半導体でも良質な単結晶膜を大きな面積で製造することが可能だという。 SiCウエハー製造技術、産学官が連携して共同研究

SiCウエハー製造技術、産学官が連携して共同研究

産業技術総合研究所(産総研)は、次世代パワー半導体用の高品質SiC(炭化ケイ素)ウエハーを低コストで製造するための技術開発に向けて、大型共同研究を始めた。ウエハーメーカーを含む民間企業17社や公的3機関と連携し開発に取り組む。 理研ら、量子ビットの電気的操作を初めて実現

理研ら、量子ビットの電気的操作を初めて実現

理化学研究所(理研)や産業技術総合研究所(産総研)らによる国際共同研究グループは、表面弾性波によって伝搬する単一電子の量子状態を制御することで、量子ビットの電気的操作を初めて実現した。 日台が連携、2nm世代に向けた「hCFET」を開発

日台が連携、2nm世代に向けた「hCFET」を開発

日本と台湾の国際共同研究グループは、2nm世代に向けた積層型Si/Ge異種チャネル相補型電界効果トランジスタ「hCFET」を開発した。