TSMCの微細化は2nmまで? 以降はパッケージングが肝に:2021 Technology Symposium(3/3 ページ)

ムーアの法則はこれまで長年にわたり、「半導体チップのトランジスタ密度は、2年ごとに2倍になる」との見解を維持してきたが、3nmプロセスにおいて数々の問題が提示されるようになった。それでもTSMCは、引き続き楽観的な見方をしているようだ。

パッケージング技術への期待

TSMCは、3nm以降のイノベーションには、新しいトランジスタ構造と材料が必要だと述べる。

同社は、従来のプロセスに比べて銅の結晶粒径を7倍以上に大きく成長させる新しいアニールプロセスにより、バックエンドのインターコネクトのブレークスルーを実現したと主張する。TSMCによると、このプロセスは配線抵抗を約30%低減し、インターコネクトの微細化の範囲を拡大するという。

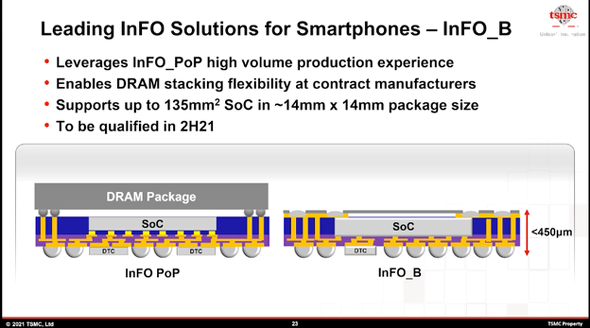

TSMCは、InFOの提供も拡張している。TSMCは、2021年後半にもスマートフォン向けの「InFO B」を認定する計画だ。Info Bは、厚さが450μm以下で、最大135mm2のサイズのモバイルSoC(System on Chip)を搭載できる。同社は、最も厳しいフォームファクター要件を満たすために、14×14mmのInFOパッケージを用意しているという。

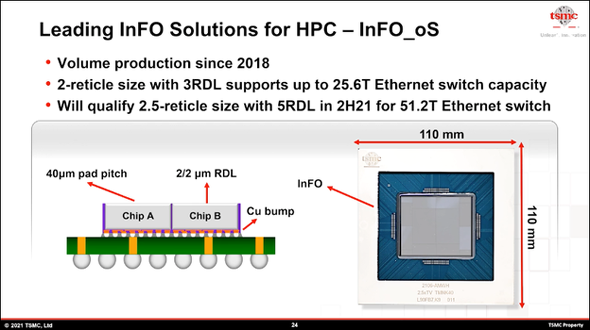

TSMCはさらに、「InFO oS(InFO on Substrate)」も提供中だ。InFO oSは、「CoWoS R」「CoWoS L」同様に、HPC(High Performance Computing)のアプリケーションに向ける。

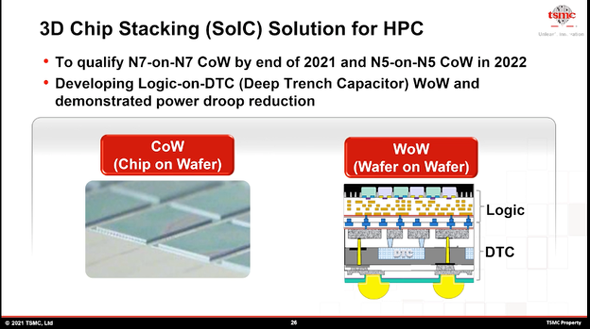

WoW(Wafer on Wafer)とCoW(Chip on Wafer)についてもアップデートがあった。CoWについては、2021年までに7nmプロセスのウエハーを利用する「N7-on-N7」を、2022年には5nmウエハーを使用する「N5-on-N5」を認定する計画だ。WoWについては、ディープトレンチキャパシター(DTC)にロジックを統合することを目指す。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

TSMCの最新プロセスまとめ、3nm以降の開発も進行中

TSMCの最新プロセスまとめ、3nm以降の開発も進行中

TSMCは2021年6月1〜2日に、自社イベント「2021 Technology Symposium」をオンラインで開催した。同イベントで発表された最新プロセスノードなどをまとめる。 IBMがプロセス開発の“契約不履行”でGFに賠償請求か

IBMがプロセス開発の“契約不履行”でGFに賠償請求か

IBMがGLOBALFOUNDRIES(GF)を契約不履行で訴え、25億米ドルの損害賠償を求めている。IBMはこの訴えをGLOBALFOUNDRIESに通告したが、米国EE Timesに対しては、まだ裁判所には提訴しておらず、従って世間に公表する準備もできていないと伝えてきた。GLOBALFOUNDRIESは既に米国ニューヨーク州最高裁判所に対し、この係属中の訴訟を価値がないものとして却下するよう申し立てを行った。 電源/接地線の埋め込みで回路ブロックの電圧降下を半分以下に低減

電源/接地線の埋め込みで回路ブロックの電圧降下を半分以下に低減

電源/接地配線を基板側に埋め込む「BPR(Buried Power Rails)」について解説する。 NXP、車載プロセッサをTSMCの16nm技術で量産

NXP、車載プロセッサをTSMCの16nm技術で量産

NXP Semiconductorsは、車載ネットワークプロセッサ「S32G2」とレーダープロセッサ「S32R294」について、TSMCの16nm FinFETプロセス技術を用いて、2021年第2四半期(4〜6月)より量産を始めた。 半導体不足は「ジャストインタイム」が生んだ弊害、TSMCが急所を握る自動運転車

半導体不足は「ジャストインタイム」が生んだ弊害、TSMCが急所を握る自動運転車

深刻な半導体不足が続く中、自動車メーカーは苦境に陥っている。だが、この苦境は自動車メーカー自らが生み出したものではないか。特に筆者は、「ジャストインタイム」生産方式が諸悪の根源だと考えている。