連載

電源供給配線網(PDN)をシリコンダイの裏面に配置して電源をさらに安定化:福田昭のデバイス通信(302) imecが語る3nm以降のCMOS技術(5)(2/2 ページ)

今回は、CMOSロジックの基本セル(スタンダードセル)に電源を分配する電源供給配線網(PDN:Power Delivery Network)のレイアウトを解説する。

BPRとBS-PDNの組み合わせが電源雑音を45%低減

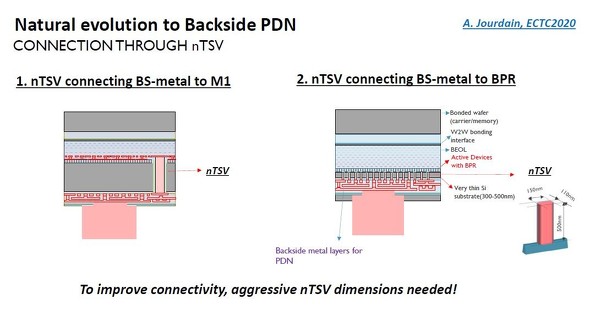

埋め込み電源線(BPR)と裏面の電源供給配線網(BS-PDN)を製造する工程は、かなり複雑だ。微細なTSV(μTSVあるはnTSV)によってBPRとBS-PDNを接続するとともに、シリコンウエハー裏面に金属配線を形成する工程が必要である。

微小なTSV(nano-TSV(nTSV))を介した裏面側配線と表面側配線の接続構造例。左は一般的な接続構造。右は裏面側配線(電源供給配線網(PDN))と埋め込み電源線(BPR)をnTSVで接続した構造。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

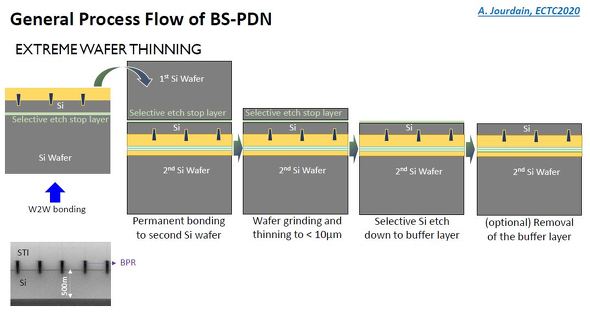

例えば、BPRを形成済みのシリコンウエハー(1stウエハー)を、別のシリコンウエハー(2ndウエハー)に貼り合わせる。それから1stウエハーを研削し、さらにはエッチングによって10μm前後にまで薄くする。

裏面側に電源供給配線網(BS-PDN)を製造する工程(前半)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

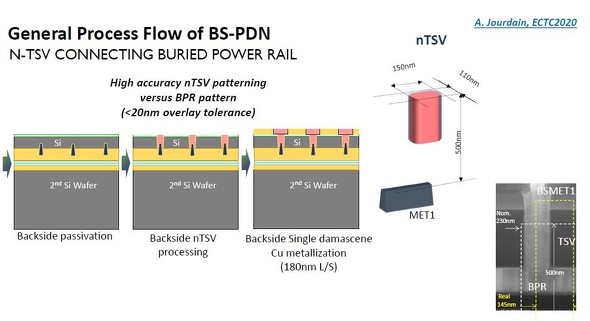

それからBPRと接続するnTSVを形成する。nTSVの埋め込み金属は銅(Cu)である。nTSVを形成後に、シングルダマシンプロセスによってCu配線層のBS-PDNを製造する。

裏面側に電源供給配線網(BS-PDN)を製造する工程(後半)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

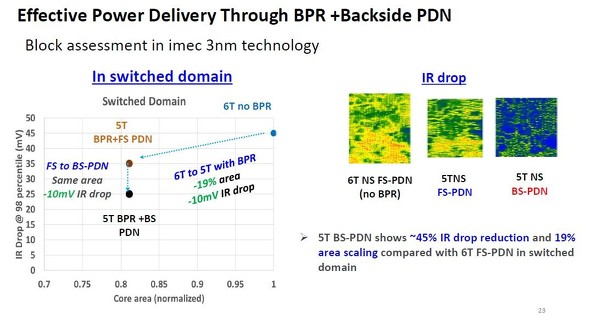

CMOSロジックの基本セル(スタンダードセル)でBPRおよびBS-PDNの効果を評価してみた。6トラック(6T)の基本セル(BPRなし、FS-PDN)を基準にすると、BPRを導入した5トラック(5T)の基本セル(FS-PDN)は回路ブロックの面積が19%減少し、電源電圧降下が45mVから35mVに減少した。ここでBS-PDNを追加すると回路ブロックの面積は変わらないものの、電源電圧降下は25mVとさらに低下した。6Tセルに比べ、電源電圧の変動を約45%に抑えられる。

BPRとBS-PDNの効果。左は回路ブロック(コア)の面積と電源電圧降下の関係。右は回路ブロックの温度分布(IRドロップの大きさを反映)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

埋め込み電源配線の構造と材料選択

埋め込み電源配線の構造と材料選択

今回は、BPR(Buried Power Rail)の複雑な構造を説明する略語を定義するとともに、金属材料の候補を解説する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。