次々世代のトランジスタ「シーケンシャルCFET」が抱える、もう1つの課題:福田昭のデバイス通信(313) imecが語る3nm以降のCMOS技術(16)(2/2 ページ)

今回は前回に続いてシーケンシャルCFETの講演部分を説明する。モノリシックCFETに比べるとシーケンシャルCFETの製造プロセスは難しくない。ただし製造プロセスには大きな制約が付きまとう。前回はその1つである、ウエハーを貼り合わせる界面で欠陥が発生する問題と対策を述べた。今回はもう1つの課題である、温度条件を解説しよう。

歪みシリコンのSOIウエハーとレーザーアニールが有望な対策に

通常のトランジスタ形成プロセスから見ると、550℃という温度条件はかなり厳しいものだ。特に問題になるのが、エクステンション(拡散層)の不純物を活性化するための熱処理(1000℃以上)と、欠陥を低減するための熱処理(900℃前後)である。これらの熱処理はいずれも、トップ側のトランジスタ形成プロセスで実施される。これらの熱処理を省くと、トランジスタ(通常、トップ側はnチャンネルMOS FET)の性能が上がらない。

講演で挙げられた対策は2つ。1つは、歪みシリコンによるnチャンネルMOS FETの性能向上である。もう1つは、レーザーによる熱処理(レーザーアニール)だ。

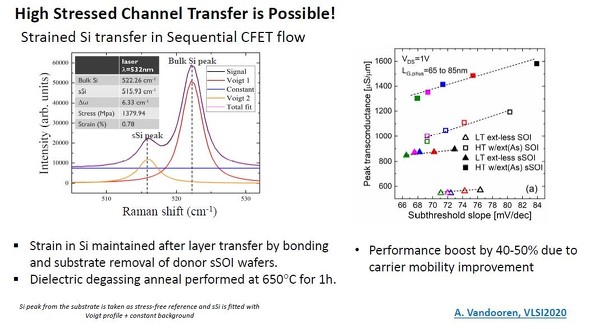

SOI(Silicon-On-Insulator)ウエハー製品の中には、表面のシリコン層に伸張応力を与えたものがある。「sSOI(strained SOI)」ウエハーと呼ばれる。このsSOIウエハーをトップ側に採用したところ、トップ側nチャンネルMOS FETのトランスコンダクタンスが40〜50%ほど向上した。エクステンションの形成プロセス(熱処理)を省いたにも関わらず、エクステンション有り(高温の熱処理あり)のトランジスタに近いトランスコンダクタンスを得た。通常のSOIウエハーをトップ側に採用してエクステンション形成を省いたトランジスタは、エクステンション有りに比べてトランスコンダクタンスの値が半分に下がっていた。

歪みシリコンSOI(sSOI)によるトランジスタの性能向上。左はウエハー貼り合わせ工程の脱ガス熱処理(650℃、1時間)を加えても歪みシリコンが維持されていることを示す分析結果(ラマン散乱分光分析)。右はnチャンネルMOSトランジスタのサブスレッショルドスロープ(SS)(横軸)とトランスコンダクタンス(ピーク値)の関係。LTは低温プロセス、HTは高温プロセス、extはエクステンション(「ext-less」はエクステンションなし、「w/ext(As)」はヒ素(As)を注入することによるエクステンションの形成を意味する)、SOIは通常のシリコンチャンネル、sSOIは歪みシリコンチャンネルを指す 出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond – device architectures, parasitics and materials」の配布資料)

エクステンション用不純物注入後のレーザーアニールには、波長が308nmのエキシマ(XeCl)レーザー(パルス周期100ナノ秒から200ナノ秒)を使用した。nチャンネルMOS FETとpチャンネルMOS FETのオン/オフ電流特性で高温スパイクアニール(従来の熱処理)とレーザーアニールを比較したところ、電流特性に目立った違いは見られなかった。

熱処理(アニール)方法によるオン/オフ電流特性の違い。左はnチャンネルMOS FET、右はpチャンネルMOS FET。縦軸はオフ電流(ゲート・ソース間電圧0V)、横軸はオン電流(ゲート・ソース間電圧1V)。LT LAは低温のレーザーアニール、HT spikeは高温のスパイクアニール、Asはヒ素、Pはリン、Bはボロンを意味する 出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond – device architectures, parasitics and materials」の配布資料)

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。