連載

シリコンダイを積層する3次元集積化技術「SoIC」:福田昭のデバイス通信(338) TSMCが開発してきた最先端パッケージング技術(11)(2/2 ページ)

今回から、シリコンダイを3次元積層する技術「SoIC(System on Integrated Chips)」を解説する。

チップとウエハー、ウエハーとウエハーの組み合わせを用意

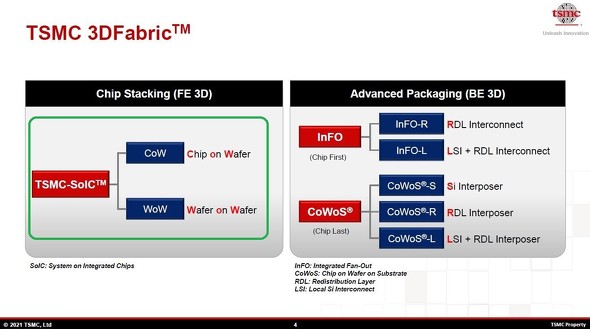

TSMCが提供する「SoIC」技術には、チップとウエハーを積層する「CoW(Chip on Wafer)」とウエハーとウエハーを積層する「WoW(Wafer on Wafer)」がある。

TSMCが提供している先進パッケージング技術「3DFabric」と「SoIC」の分類(左の緑色の線で囲んだ部分)[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)、緑色の線は筆者が記入したもの

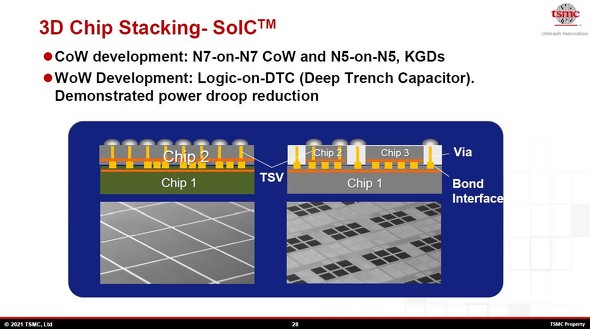

「CoW」は、例えば同一のCMOSロジック製造プロセスで生産した、異なる大きさのシリコンダイを重ねて接続する。通常は大きなシリコンダイの上に複数の小さなシリコンダイを搭載する。7nmプロセスのシリコンダイで最初に提供し、続いて5nmプロセスのシリコンダイでも提供する予定だ。

「CoW(Chip on Wafer)」と「WoW(Wafer on Wafer)」の開発状況。下側の断面構造図は左がWoW[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

「WoW」は、ウエハーレベルでシリコンダイを積層する。上下のシリコンダイは同じ寸法である。例えば下側を溝形キャパシタのアレイを作り込んだダイ、上側にロジックダイをレイアウトする。こうするとロジックダイの電源系を同時スイッチングに対して安定化できる。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Siインターポーザを樹脂基板に変更した低コスト版の「CoWoS」

Siインターポーザを樹脂基板に変更した低コスト版の「CoWoS」

今回からは「CoWoS」の派生品である「CoWoS_R(RDL Interposer)」と「CoWoS_L(Local Silicon Interconnect + RDL Interposer)」の概要を解説する。 ハイブリッド型トランジスタ、GaNとSiCを一体化

ハイブリッド型トランジスタ、GaNとSiCを一体化

産業技術総合研究所(産総研)は、GaNを用いたトランジスタとSiCを用いたPNダイオードをモノリシックに集積したハイブリッド型トランジスタを作製し、動作実証に成功したと発表した。GaNとSiCの特長である、低オン抵抗と非破壊降伏の両立を可能とした。 ウエハースケールの超巨大プロセッサを実現した「InFO」技術

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

「InFO」技術を改良した2種類のパッケージのうち、ウエハー規模の巨大なパッケージング技術「InFO_SoW」を解説する。 モバイル向け小型薄型パッケージ「InFO」が進化

モバイル向け小型薄型パッケージ「InFO」が進化

TSMCが開発してきた先進パッケージング技術の最新動向を紹介する。始めは全体のトレンドを示す。 「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。