シリコンダイを直接水冷する「SoIC」向けの放熱技術:福田昭のデバイス通信(341) TSMCが開発してきた最先端パッケージング技術(14)

前回に続き、放熱技術について解説する。TSMCは同技術を「ISMC(Integrated Si Micro-Cooler)」と呼ぶ。

シリコンダイの表面を機械加工して冷却水を通す

高性能プロセッサとその関連技術に関する国際学会「Hot Chips」が昨年(2021年)8月22日〜24日にオンラインで開催された。「Hot Chips」は高性能プロセッサの最新技術情報を入手できる貴重な機会として知られている。会期は3日間で、初日が「チュートリアル(Tutorials)」と呼ぶ技術講座、2日目と3日目が「カンファレンス(Conference)」と呼ぶ技術講演会となっており、講演会とは別にポスター発表の機会も用意される。オンライン開催となったことしは、あらかじめ録画されたビデオをプログラムに沿って公開する形式となった。参加登録者は開催後も一定の期間は、オンデマンドで講演を聴講できる。

初日の「チュートリアル(Tutorials)」では、13件の講演が実施された。その中で「先進パッケージング技術」に関する講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」が極めて興味深かった。講演者はTSMCで研究開発担当バイスプレジデント(現在はシステム集積化手法開発担当バイスプレジデント)をつとめるDouglas Yu氏である。

そこで本講演の概要を第328回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン。前回から3番目のパート「New Heterogeneous Integrations」の講演部分を説明している[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

前回から、異種のデバイスを集積化する技術に関する講演(「New Heterogeneous Integrations」)部分の紹介を始めた。講演で説明した技術は2つ。最初が放熱(冷却)技術、次がシリコンフォトニクス技術である。前回では既存の主要な放熱技術を簡単に解説するとともに、3次元積層モジュール「SoIC」に向けた高性能冷却技術のコンセプトを述べた。

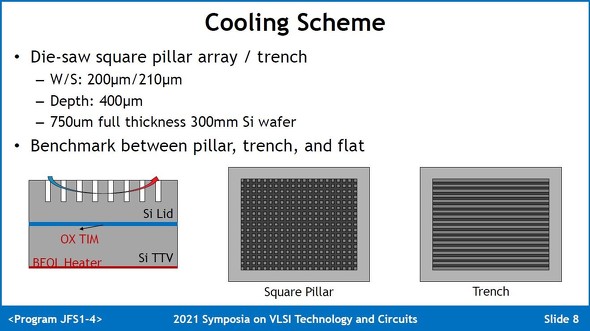

開発中の高性能冷却技術をTSMCは「ISMC(Integrated Si Micro-Cooler)」と呼んでいる。ISMCの考え方は単純で、放熱用シリコンダイの表面に冷却水を流すことで高い放熱性能を得る。シリコンダイの表面には、溝(トレンチ)あるいは柱(ピラー)のアレイを形成しておく。こうするとシリコンダイの表面積、すなわち冷却水と接触する領域が拡大し、放熱性能が大幅に高まる。

放熱用シリコンダイによる水冷の概要。放熱用シリコンダイの表面に細長い柱(ピラー)のアレイ、あるいは溝(トレンチ)のアレイを形成し、冷却水を流す[クリックで拡大] 出所:TSMC(2021 VLSI Technology Symposiumの講演「Ultra High Power Cooling Solution for 3D-ICs」(講演番号JFS1-4)のスライドから)

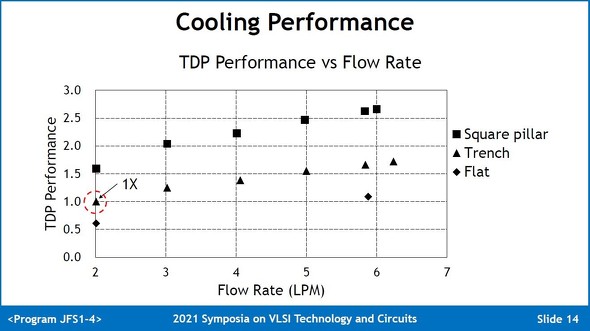

角柱のアレイを形成することでTDPが2.5倍に向上

TSMCは、放熱用シリコンダイの表面が無加工(平面(Flat))の場合と、溝(Trench)のアレイを形成した場合、断面が四角い柱(Square pillar)のアレイ(角柱のアレイ)を形成した場合で熱設計電力(TDP:Thermal Design Power)を比較した。冷却水の流量が毎分2リットル(2LPM(liters per minute))で溝のアレイを形成した場合のTDPを「1」とすると、同じ流量で平面の場合は「約0.6」に低下し、角柱のアレイを形成した場合は「約1.6」に上昇する。

冷却水の流量を毎分6リットル(6LPM)に増やすと、平面のTDPは「約1.0」に、溝アレイのTDPは「約1.7」に、角柱アレイのTDPは「約2.5」に上昇する。流量を増やすことよりも、表面を加工することの効果が大きいことが分かる。

冷却水の流量(LPM)と熱設計電力(TDP)の関係。放熱用シリコンダイの表面形状で比較した[クリックで拡大] 出所:TSMC(2021 VLSI Technology Symposiumの講演「Ultra High Power Cooling Solution for 3D-ICs」(講演番号JFS1-4)のスライドから)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

「InFO」技術を改良した2種類のパッケージのうち、ウエハー規模の巨大なパッケージング技術「InFO_SoW」を解説する。 モバイル向け小型薄型パッケージ「InFO」が進化

モバイル向け小型薄型パッケージ「InFO」が進化

TSMCが開発してきた先進パッケージング技術の最新動向を紹介する。始めは全体のトレンドを示す。 「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。 欧州が欧州半導体法「European Chips Act」の策定へ

欧州が欧州半導体法「European Chips Act」の策定へ

欧州委員会委員長であるUrsula von der Leyen氏が2021年9月15日(現地時間)、一般教書演説の中で、「European Chips Act(欧州半導体法)」の策定に関する発表を行った。中国政府が半導体イノベーションに数十億米ドル規模の資金を投じていることや、米国議会が半導体の戦略的価値について合意に達したことなどを受け、EUは、主体的な最先端技術の実現を目指す法案を策定し、競争に参入していく考えを表明した。 第4世代R-Car SoCも発表、ルネサスが語る車載戦略

第4世代R-Car SoCも発表、ルネサスが語る車載戦略

ルネサス エレクトロニクスは2021年10月6日、オンラインで記者説明会を実施。同社オートモーティブソリューション事業本部の事業本部長、片岡健氏が車載事業戦略について語った。