複数AIアクセラレータ搭載チップ、動作を確認:開発に評価プラットフォーム活用

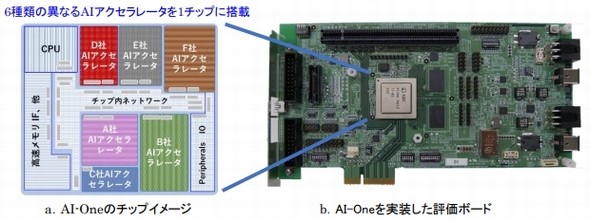

新エネルギー・産業技術総合開発機構(NEDO)らは、仕様が異なる6種類のAIアクセラレータを搭載した実証チップ「AI-One」を試作し、設計通りの周波数で動作することを確認した。AIアクセラレータ向け評価プラットフォームを活用することで、従来に比べAIチップの開発期間を45%以下に短縮できるという。

従来に比べ45%以下の期間でAIチップの設計、評価が可能に

新エネルギー・産業技術総合開発機構(NEDO)は2022年3月、産業技術総合研究所(産総研)や東京大学と共同で、仕様が異なる6種類のAIアクセラレータを搭載した実証チップ「AI-One」を試作し、設計通りの周波数で動作することを確認したと発表した。NEDOなどが用意したAIアクセラレータ向け評価プラットフォームを活用することで、従来に比べAIチップの開発、評価期間を45%以下に短縮できるという。

NEDOは、「AIチップ開発加速のためのイノベーション推進事業」に取り組んでいる。その一環として、産総研や東京大学と共同で東京大学浅野キャンパス内に、中小・ベンチャー企業などが行うチップ開発を支援する「AIチップ設計拠点」を設けた。

この拠点では、半導体設計に必要となる共通基盤技術の開発や回路設計用EDAツール、標準IPコアなどを用意し、「AIアクセラレータ開発に向けた評価プラットフォーム」として、ベンチャー企業などに提供している。

今回は、同評価プラットフォームを実証するため、ベンチャー企業らの協力を得て、6種類の独自AIアクセラレータを1チップに搭載したAI-Oneを設計。外部に製造を委託し、28nmCMOSプロセスを用いて実チップを試作した。そして、これら全てのAIアクセラレータが設計通りの周波数で動作することを確認した。

具体的には、下記の項目についてその動作を確認した。

(1)AI-Oneに組み込んだCPUの800MHz動作において、各AIアクセラレータからLPDDR4メモリに対しフルバンド幅(毎秒24.8GB)でデータを転送。

(2)CPUからLPDDR4メモリに対し、SoC評価時に求められる安定した読み書き動作。

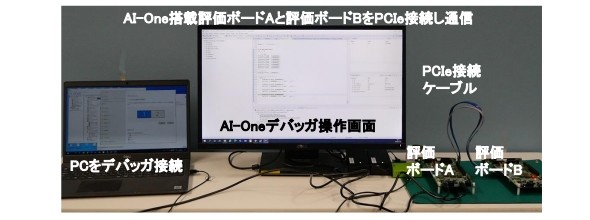

(3)PCIe Gen3プロトコル8Gビット/秒での通信とプログラム制御、基板上のフラッシュメモリに書き込んだプログラムからQSPI25MHzでのブートとLPDDR4の起動、DFT機能による内蔵メモリやロジック回路およびPLLの動作、CPUから各AIアクセラレータのレジスターアクセスと割り込み、クロック周波数変更時のAIアクセラレータ動作。

今回、AI-Oneの設計に協力したベンチャー企業などは、試作した各AIアクセラレータの消費電力や性能などについて、さらに詳細な評価を行う。NEDOと産総研、東京大学は、参加企業からのフィードバックに基づき、さらに使いやすいエッジ向けAIチップの評価プラットフォームを確立していく計画である。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

NEC、LHZ方式の基本ユニットを開発し動作を実証

NEC、LHZ方式の基本ユニットを開発し動作を実証

NECは、超伝導パラメトロンを用い、多ビット化が容易なLHZ方式の基本ユニットを世界で初めて開発し、アニーリング動作の実証に成功した。量子アニーリングマシンの実現に向けて、開発を加速する。 SteraVision、可動部のない自動運転用LiDARを開発

SteraVision、可動部のない自動運転用LiDARを開発

SteraVisionは、可動部がない自動運転用の「ソリッドステートLiDAR」を開発した。LiDARによる物体検出と3Dカメラ画像を融合させ、自動運転車向け認識技術(パーセプションAI)と連動させることにより、人間の目のような機能を持った視覚システムを実現できるという。 MEMS技術を用い電子部品の薄型・小型化を実現

MEMS技術を用い電子部品の薄型・小型化を実現

新エネルギー・産業技術総合開発機構(NEDO)とアルファー精工、旭電化研究所および、シナプスは、MEMS技術を用い、薄型かつ小型で優れた伝送特性を備えた電子部品の開発に成功した。素材として金属と樹脂を用いるため、第6世代移動通信(6G)システム向けのコネクターやソケットなどに適用することができる。 スマホでAI処理を行うプロセッサアーキテクチャ

スマホでAI処理を行うプロセッサアーキテクチャ

東京工業大学は、高度なAI処理をスマートフォンなどで実行できる「プロセッサアーキテクチャ」を開発した。試作したチップの実効効率は最大26.5TOPS/Wで、世界トップレベルだという。 光ICと光ファイバー間の3次元光配線技術を開発

光ICと光ファイバー間の3次元光配線技術を開発

新エネルギー・産業技術総合開発機構と技術研究組合光電子融合基盤技術研究所は、光ICと光ファイバー間の3次元光配線技術を開発した。開発した試作品を用い、85℃の高温環境下で毎秒112Gビットの高速光伝送に成功した。 複数AIアクセラレーター搭載の評価チップを試作

複数AIアクセラレーター搭載の評価チップを試作

新エネルギー・産業技術総合開発機構(NEDO)と産業技術総合研究所(産総研)および、東京大学は共同で、仕様が異なる6種類のAIアクセラレーターを搭載した評価チップ「AI-One」を設計、試作を始めた。これを活用すると、短い期間で安価にAIチップの設計と評価が可能になる。