RISC-Vに舵を切ったMIPS、新型コア2製品を発表:高性能プロセッシングを狙う(2/2 ページ)

MIPSが2022年5月、高性能プロセッシングをターゲットとするRISC-Vベースの新製品を発表し、大きな注目を集めている。同社にとって初となるRISC-VベースのマルチプロセッサIP(Intellectual Property)コア「eVocore P8700」と「eVocore I8500」を提供するという。

MIPSは「新たな進化を遂げようとしている」

MIPSは今回、イスラエルで2022年5月10日(現地時間)に開催された「ChipEx 2022」において詳細を発表した。同社のセールス&マーケティング部門担当バイスプレジデントを務めるItai Yarom氏は、米embedded.comのインタビューの中で、「MIPSは、新たな進化を遂げようとしている。RISC-V ISAに注力する方向へと転換したことにより、MIPSマイクロアーキテクチャを数十億台規模の製品で実証し、それをさらに強化していきたい考えだ。当社がRISC-Vを選んだ背景には、ソフトウェアの導入コストが低いため、顧客向けの製品開発を加速させることが可能だという理由がある」と述べている。

また同社のCEO(最高経営責任者)であるDesi Banatao氏は、「MIPSは、RISC-Vへの移行に伴い、プロセッサ市場の高性能分野をターゲットに定めていく。リアルタイム機能やハードウェア仮想化、機能安全性、セキュリティ技術などで差別化することにより、自動車やエッジコンピュータ、ネットワーキング、スイッチング、大規模コンピューティングシステムなどの分野に向けて、魅力的な製品を提供できるようになる」と付け加えた。

Semico ResearchでASIC/SoC(System on Chip)分野の主席アナリストを務めるRich Wawrzyniak氏は、「さまざまなメーカーが、オープンソフトウェア開発環境において実現可能な、差別化の可能性を見いだしていることから、今後も引き続き、自動車などの分野においてRISC-Vの導入が進んでいくだろう。MIPSは、長年にわたってRISCアーキテクチャおよびコアを提供してきた実績がある他、自動車やネットワーキング、高性能アプリケーションなどの分野でも力強い足跡を残してきたことから、同社にとってRISC-Vへの移行は、次の成長段階へと進んでいく上で理にかなっていると言える」と述べる。

MIPSはインタビューの中で、高性能分野をターゲットに定めていくことを明言した。Yarom氏は、「MIPSのフラグシッププロセッサであるeVocore P8700は既に、自動車分野のデザインウィンを獲得している。シングルスレッド/マルチスレッドのオプションを用意していて、他のRISC-Vベースのプロセッサと比べて、少なくとも2倍高い性能を提供することが可能だ。RISC-Vで高性能を実現するには、効率的な方法でシステムを構築してメモリ/帯域幅を確保する必要があるため、決してささいな事ではない。当社の新しいeVocoreは、さらなる高性能化を実現することによって、RISC-Vコミュニティーをサポートすることが可能だ」と述べている。

RISC-V Internationalも歓迎

RISC-V Internationalは、MIPSが新たな方向に舵を切ったことを非常に歓迎している。CEOを務めるCalista Redmond氏は、「われわれとしては、RISC CPUアーキテクチャのパイオニアの1社であるMIPSが、RISC-Vに目を向けていることを非常にうれしく思っている。MIPSはこれまで長年にわたり、ハイエンドコンピューティングで採用されてきたが、これはRISC-Vがまさに今、大きなけん引力を獲得し始めたばかりの分野だ。MIPSは、RISC-VコミュニティーにCPUイノベーションの伝統をもたらし、柔軟性/拡張性を実現可能な、RISC-Vとの互換性を持つ新しいCPUを提供してくれる」と述べている。

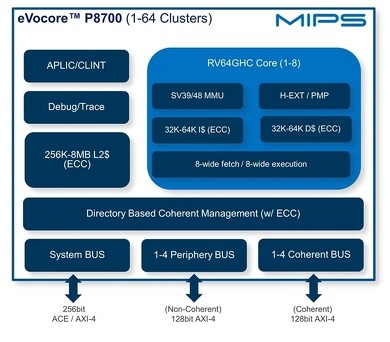

eVocore P8700は、スーパースカラー性能を提供することが可能なマルチプロセッシングシステムだ。マルチイシューアウトオブオーダー(OoO)実行を実装したディープパイプラインと、マルチスレッディングとを組み合わせることで、優れた計算スループットを実現する。そのシングルスレッド性能は、他のRISC-V CPU IP製品を大きく上回り、最大で64クラスタ、512コアまで可能。eVocore P8700は、2022年第4四半期に提供開始予定だという。

一方、eVocore I8500は、SoCアプリケーション向けに最高クラスの電力効率を実現可能な優れたマルチプロセッシングシステムだ。各コアで、マルチスレッドと、高効率のトリプルイシューのパイプラインとを組み合わせることにより、高い計算スループットを提供することができるとする。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Wave Computingが破産、「MIPS」として事業継続へ

Wave Computingが破産、「MIPS」として事業継続へ

Wave Computingは、米連邦破産法11条の手続きを終え、MIPSとして引き続き事業を継続する予定であることを明らかにした。 MIPS、オープンソース化で「RISC-V」越えを狙う?

MIPS、オープンソース化で「RISC-V」越えを狙う?

MIPSアーキテクチャのISA(命令セット)をオープンソース化する方針を発表したWave Computing。しかし、オープンソース化を実現するということは、長い間慣れ親しんできた既存のIP(Intellectual Property)ライセンスビジネスであるMIPSから、大きく移行することを意味する。 マイコンからHPCまで――RISC-Vが目指す“懐の深さ”

マイコンからHPCまで――RISC-Vが目指す“懐の深さ”

2017年12月18日に、「RISC-V Day 2017 Tokyo(リスクファイブの1日)」が開催され、RISC-V会長のKrste Asanović氏らがRISC-Vについて講演を行った。本記事では、基調講演を一部抜粋して紹介する。 MIPSコンピュータをめぐる栄枯盛衰

MIPSコンピュータをめぐる栄枯盛衰

RISCプロセッサの命令セットアーキテクチャである「MIPS」。そのMIPSを採用したワークステーションの開発には、日本企業も深く関わった、栄枯盛衰の歴史がある。 ルネサスの汎用MPU、64ビットRISC-V コアを搭載

ルネサスの汎用MPU、64ビットRISC-V コアを搭載

ルネサス エレクトロニクスは、64ビットRISC-V CPUコアを搭載した汎用MPU「RZ/Five」のサンプル出荷を始めた。IoTエッジデバイスに向けて性能や機能を最適化している。