次々世代のトランジスタ「シーケンシャルCFET」の製造プロセス:福田昭のデバイス通信(312) imecが語る3nm以降のCMOS技術(15)

今回は、下側(底側、ボトム側)のトランジスタを作り込んでから、その上に別のウエハーを貼り合わせて上側(頂側、トップ側)のトランジスタを作成する「シーケンシャル(Sequential)CFET」の製造プロセスを解説する。

コンプリメンタリFET(CFET)を製造するもう1つの方法

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

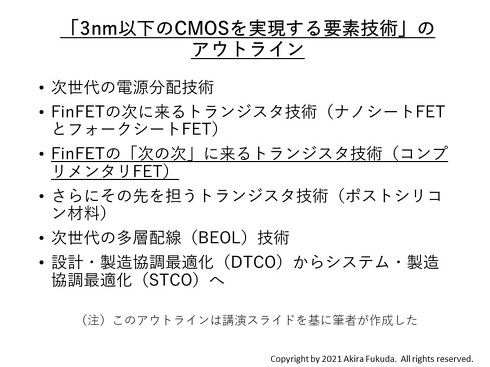

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。本シリーズの第11回から「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している(クリックで拡大)

本シリーズの第11回から、3番目のパートである「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している。前々回(第13回)では、「コンプリメンタリFET(C(Complementary)FET)」は製造方法の違いによって2種類に分けられると述べた。1つは、成膜工程やエッチング工程、拡散工程、平坦化工程などを繰り返して2つのトランジスタ(ボトム側トランジスタとトップ側トランジスタ)を積み上げる「モノリシック(Monolithic)CFET」である。前回(第14回)は、このモノリシックCFETの製造プロセスを説明した。

今回は、下側(底側、ボトム側)のトランジスタを作り込んでから、その上に別のウエハーを貼り合わせて上側(頂側、トップ側)のトランジスタを作成する「シーケンシャル(Sequential)CFET」の製造プロセスを解説しよう。

「モノリシック(Monolithic)CFET」(左)と「シーケンシャル(Sequential)CFET」(右)の概要。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

シーケンシャルCFET製造のカギはウエハーの貼り合わせ

シーケンシャルCFETの製造は以下のように進む。始めはボトム側のトランジスタを形成する。それからシリコン酸化(SiO2)膜で表面全体を被覆する。CMP(Chemical Mechanical Polishing)によってシリコン酸化膜を約30nmの厚みになるまで削るとともに平坦化する。

この工程とは別に、表面をシリコン酸化膜で被覆したシリコンウエハーを用意する。このウエハーのシリコン酸化膜を下にして、ボトム側のトランジスタを形成済みのウエハーと貼り合わせる。それから上のウエハーにトップ側のトランジスタを作り込む。

シーケンシャル(Sequential)CFETの製造工程(一部のみ)(左)とトランジスタの性能(右)。シリコン酸化膜を厚くすると、トランジスタの動作周波数(厳密にはリング発振器の発振周波数)が低下する。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

ここで課題となるのが、ウエハー同士の貼り合わせによって界面に発生する欠陥の低減である。貼り合わせの表面にあるシリコン酸化膜を厚くすると欠陥は減るものの、トランジスタの性能(動作速度)が低下する。逆にシリコン酸化膜を薄くすると、トランジスタの性能は向上するものの、欠陥が増加する。

講演では、ボトム側とトップ側でシリコン酸化膜の厚みを変え、ウエハーの貼り合わせによる欠陥(ボイド)の発生状態を顕微鏡で観察した画像を示していた。ボトム側の膜厚は「薄い」「中間」「厚い」の3段階。接合部の膜厚は「15nm」「35nm」「85nm」の3段階である。

シリコン酸化膜(誘電膜)の厚みと、ウエハーの貼り合わせによる欠陥(ボイド)発生の関係。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

「35nm」の条件だと、「薄い」との組み合わせではボイドがウエハー全体に発生した。「中間」との組み合わせでは、ボイドはウエハーの周縁部(エッジ)だけに減った。「厚い」との組み合わせでは、ボイドが発生しなかった。目標とする酸化膜厚を達成できたとする。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。