ALD法で酸化物半導体を三次元構造へ均一に成膜:高密度FeFETメモリの実現へ

東京大学と奈良先端科学技術大学院大学の共同研究グループは、酸化インジウムの成膜に原子層堆積(ALD)法を用いる技術を開発、この技術を活用して三次元垂直チャネル型の強誘電体/反強誘電体トランジスタメモリを開発した。

三次元垂直チャネル型強誘電体/反強誘電体トランジスタメモリを開発

東京大学生産技術研究所の小林正治准教授と奈良先端科学技術大学院大学の浦岡行治教授らによる共同研究グループは2022年6月、酸化インジウム(In2O3)の成膜に原子層堆積(ALD)法を用いる技術を開発、この技術を活用して三次元垂直チャネル型の強誘電体/反強誘電体トランジスタメモリを開発したと発表した。

ビッグデータを有効に利活用するには、クラウドサーバだけに頼らず、IoT機器でも大量のデータを蓄積し、端末側でAI処理を行うことが求められている。これを実現するには、より大容量で消費電力は極めて小さいストレージメモリが必要になるという。

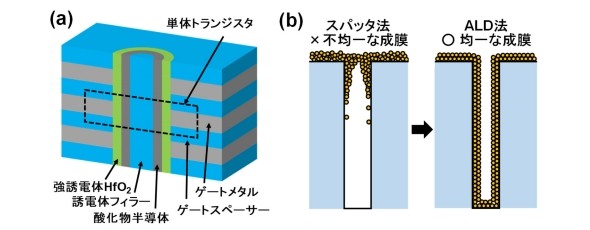

こうした中で小林氏らは、IGZOなどの酸化物半導体をチャネルとする強誘電体トランジスタ(FeFET)メモリを提案し、その実現可能性と有用性を理論的に示してきた。ところが、従来のスパッタ法による成膜では、三次元構造にIn2O3などの酸化物半導体薄膜を均一に形成するのが難しかったという。

そこで共同研究グループは、ALD法を用いることでIn2O3の成膜を均一に行う技術を開発した。ALD法で成膜をしたIn2O3を用い、薄膜トランジスタを作製したところ、その移動度は40cm2/Vsを超えた。ALD法を用いると三次元構造に対してもIn2O3薄膜を均一に形成できることを確認した。

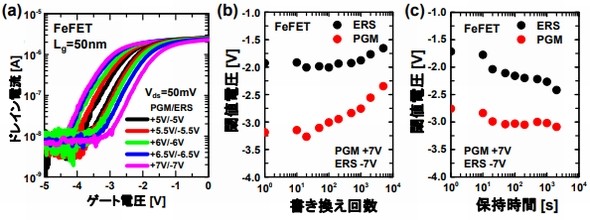

また、ALD法で成膜ができる「二酸化ハフニウムジルコニウム(HfZrO2)」強誘電体をゲート絶縁膜とするFeFETを試作した。このFeFETは理論的な予測値の通り、1.5V程度のメモリウィンドウ(閾値電圧差)、104回を超える書き換え耐性、103秒を超える保持特性を有していることが分かった。

試作した三次元垂直チャネル型FeFETの特性。左はドレイン電流−ゲート電圧特性。中央はプログラム(PGM)パルス電圧と消去(ERS)パルス電圧を交互に印加した時の、FeFETにおける閾値変動を表す書き換え耐性。右はPGMまたはERSパルス電圧を印加した後の、FeFETにおける閾値電圧の安定性を表す保持特性 出所:東京大学他

さらに今回は、反強誘電体の「ZrO2」をゲート絶縁膜とする反強誘電体トランジスタ(AFeFET)も提案した。反強誘電体を用いることで、少数キャリアを誘起しなくても効率的に消去動作が可能となり、消去状態の保持特性を改善できるという。実験により、0.7V程度のメモリウィンドウ、104回を超える書き換え耐性、103秒を超える保持特性が得られることを確認した。

試作した三次元垂直チャネル型AFeFETの特性。左はドレイン電流−ゲート電圧特性。中央はプログラム(PGM)パルス電圧と消去(ERS)パルス電圧を交互に印加した時の、AFeFETにおける閾値変動を表す書き換え耐性。右はPGMまたはERSパルス電圧を印加した後の、AFeFETにおける閾値電圧の安定性を表す保持特性 出所:東京大学他

共同研究チームは今後、多元素系酸化物半導体についても、ALD法で成膜をするための技術開発に取り組む。高移動度で高信頼の酸化物半導体についても、三次元構造への均一な成膜を目指す。さらに、ゲート、ソース、ドレインでの寄生抵抗を低減する設計とプロセスインテグレーションにより、書き換え速度を実用レベルに引き上げていく計画である。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

生体呼気で個人認証、東京大らが原理実証に成功

生体呼気で個人認証、東京大らが原理実証に成功

東京大学と九州大学、名古屋大学および、パナソニック インダストリーの研究グループは、「生体呼気」で個人認証を行う原理実証に成功した。20人を対象に行った実験では、97%以上の精度で個人を識別できたという。【訂正あり】 深層強化学習法により、超音波モーターを最適制御

深層強化学習法により、超音波モーターを最適制御

東京大学は、深層強化学習法を用いて、超音波モーターを最適駆動する制御システムを開発した。超音波モーターを手術ロボティックスや触覚提示システムなどへ搭載することが可能になるという。 東京大ら、トポロジカル導波路の広帯域化を可能に

東京大ら、トポロジカル導波路の広帯域化を可能に

東京大学と慶應義塾大学、電磁材料研究所の研究グループは、ENZ特性を持つ磁気光学材料を用いることで、帯域が広いトポロジカル導波路を実現できることを明らかにした。光回路のさらなる高密度高集積化が可能となる。 東京大ら、テラヘルツ領域の光起電力効果を観測

東京大ら、テラヘルツ領域の光起電力効果を観測

東京大学と理化学研究所らの研究グループは、強誘電体「BaTiO3(チタン酸バリウム)」を用い、テラヘルツ光照射による光電流の観測に成功した。可視光の約1000分の1の光エネルギーで発電が可能になるという。 新手法で燃料電池触媒のORR活性を2倍以上に向上

新手法で燃料電池触媒のORR活性を2倍以上に向上

量子科学技術研究開発機構(量研)と東京大学、日本原子力研究開発機構らの研究グループは、燃料電池自動車(FCV)の動力源となる固体高分子形燃料電池(PEFC)の触媒性能を、2倍以上も向上させる新たな手法を開発した。 結晶対称性を反映した新原理の超伝導整流現象を発見

結晶対称性を反映した新原理の超伝導整流現象を発見

東京大学の研究グループは、埼玉大学や東京工業大学のグループと共同で、空間反転対称性の破れた超伝導体「PbTaSe2」において、外部磁場がなくても巨大な整流特性を示すことを発見し、その微視的な機構を明らかにした。