第3世代SiC MOSFET、スイッチング損失を大幅削減:新たなデバイス構造を開発

東芝デバイス&ストレージは、同社として3世代目になる「SiC(炭化ケイ素)MOSFET」を開発し、2022年8月下旬から量産を始める。同社第2世代製品に比べスイッチング損失を約20%削減できることを確認した。

SBDを配置する構造を適用、安定した動作を確認

東芝デバイス&ストレージは2022年7月、同社として3世代目になる「SiC(炭化ケイ素)MOSFET」を開発し、2022年8月下旬から量産を始めると発表した。同社第2世代製品に比べスイッチング損失を約20%削減できることを確認した。

新製品は、従来のSiC MOSFET内部に、SBD(ショットキーバリアダイオード)をPNダイオードと並列に配置する構造にしたことで、SiCデバイスとしての信頼性を向上させた。その半面、単位面積当たりのオン抵抗(RonA)が増加したり、性能指数(Ron*Qgd)が大きくなって損失が増加したり、オン抵抗(Ron)を小さくするためにチップ面積が大きくなったりするなど、課題もあったという。

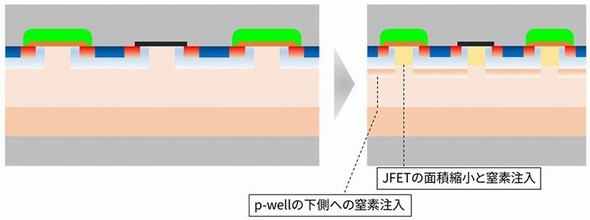

これらの課題を解決するため同社は、新たなデバイス構造を開発した。まず、SiC MOSFETのp型の広い拡散領域(p-well)の下側に窒素を注入した。これにより、広がり抵抗(Rspread)を削減し、SBDの電流を増加させた。また、JFET領域にも窒素を注入し、JFETの面積を小さくした。これにより、RonAを上げることなく帰還容量を小さくすることができたという。

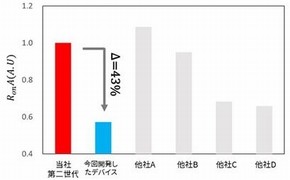

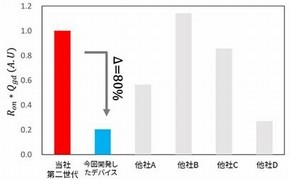

第3世代のSiC MOSFETは、新たに開発したデバイス構造を用いることで、第2世代品と比べRonAを43%も削減した。Ron*Qgdも80%削減し、スイッチング損失を約20%削減できることを試作チップで実証した。しかも、SBDを配置したことでRonAの変動が起きず、安定した動作が得られることを確認したという。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

東芝、ダブルゲート構造の逆導通型IEGTを開発

東芝、ダブルゲート構造の逆導通型IEGTを開発

東芝デバイス&ストレージと東芝は、ダブルゲート構造を採用することでスイッチング損失を低減した、耐圧4500Vの逆導通型IEGT(電子注入促進型絶縁ゲートトランジスタ)を開発したと発表した。2025年以降の実用化を目指す。 東芝が物体検出AIを開発、画像1枚を登録するだけ

東芝が物体検出AIを開発、画像1枚を登録するだけ

東芝は、未学習の物体が映った画像1枚を登録すれば、新規の物体でも高い精度で検出できる画像認識AI「Few-shot物体検出AI」を開発した。製造現場や流通現場での活用に向けて、2023年度中の製品化を目指す。 東芝、インフラ点検向けの「AI技術」を開発

東芝、インフラ点検向けの「AI技術」を開発

東芝は、数枚の正常画像と点検で得られた画像を用い、異常個所を高い精度で検出できるインフラ点検向けの「AI技術」を開発した。危険な場所にある鉄塔や橋などを点検する作業の省人化や、異常箇所の早期発見が可能となる。 東芝D&S、32ビットマイコン群に21製品を追加

東芝D&S、32ビットマイコン群に21製品を追加

東芝デバイス&ストレージは、Arm Cortex-M3コアを搭載した32ビットマイコン「TXZ+ファミリー アドバンスクラス」として、「M3Hグループ」21製品の量産を始めた。民生機器や産業機器におけるメイン制御、モーター制御などの用途に向ける。 手のひらサイズで計測距離300mの「LiDAR」を開発

手のひらサイズで計測距離300mの「LiDAR」を開発

東芝は、大きさが手のひらサイズで最長300mの距離計測を可能にする「LiDAR」を開発した。投光器を小型にできる「モジュール実装技術」および、全ての投光器を同じ向きにそろえる「モーター制御技術」を新たに開発することで実現した。 東北大ら、サマリウム鉄系等方性ボンド磁石を開発

東北大ら、サマリウム鉄系等方性ボンド磁石を開発

東北大学と東芝は、サマリウム鉄系等方性ボンド磁石を開発した。従来のネオジムボンド磁石に比べ、レアアースの使用量が半分で済み、同等の磁力を達成した。耐熱性や生産性にも優れており、車載用小型モーターなどの用途に向ける。