CPU/GPUとメモリを3次元実装、東工大などが開発:大容量データを低電力で伝送可能

東京工業大学は、CPU/GPUとメモリを3次元実装するハイブリッド3次元実装技術「BBCube 3D」を開発した。CPU/GPUとメモリ間で、大容量データを低電力で伝送することが可能となる。

DDR5と比較しデータ伝送の帯域幅は13倍、消費電力は20分の1に

東京工業大学科学技術創成研究院異種機能集積研究ユニットの大場隆之特任教授らは2023年7月、CPU/GPUとメモリを3次元実装するハイブリッド3次元実装技術「BBCube 3D」を開発したと発表した。CPU/GPUとメモリ間で、大容量のデータを低電力で伝送することが可能となる。

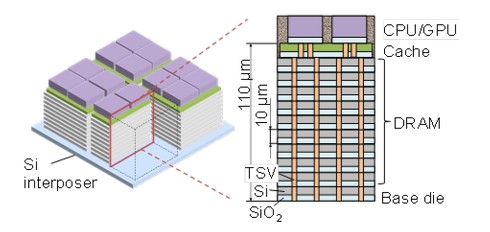

今回の研究は、東京工業大学を中心とする産学研究プラットフォーム「WOWアライアンス」と共同で行った。BBCube 3Dは、バンプレスCOW(Chip-on-Wafer)やWOW(Wafer-on-Wafer)プロセスによって、CPU/GPUとメモリを3次元積層する技術。配線にCu(銅)を採用し、埋め込み・研磨によって垂直配線を行う「CuダマシンTSV(Through Si Via)配線」を用いることで、バンプレス化に成功した。

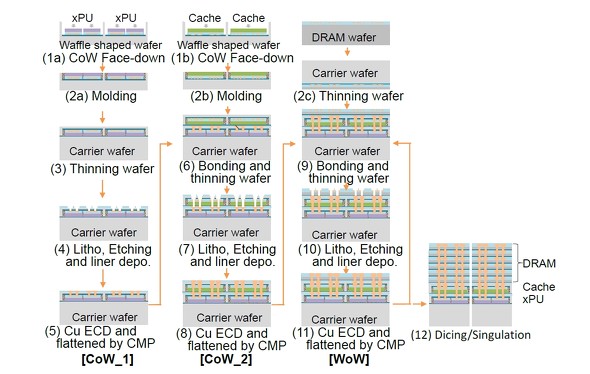

具体的なバンプレスCOWとWOWの製造プロセスはこうだ。ワッフル状のウエハーにCPUまたはGPUのチップを搭載してモールディングをする。このウエハーを薄くしてTSVを形成する。同じようにして、キャッシュチップをワッフルウエハーに搭載してモールディング。これをCPU/GPUのウエハーに積層して薄くする。その後、TSVを形成してCPU/GPUとキャッシュを接続する。

DRAMウエハーは、キャリアウエハーに貼りつけた後に薄くして、CPU/GPUやキャッシュを搭載したウエハーに積層する。その上で、TSVを形成しキャッシュとDRAMを接続する。必要な容量のDRAMウエハーを積層した後、個別に切断し最終的なチップに仕上げる。

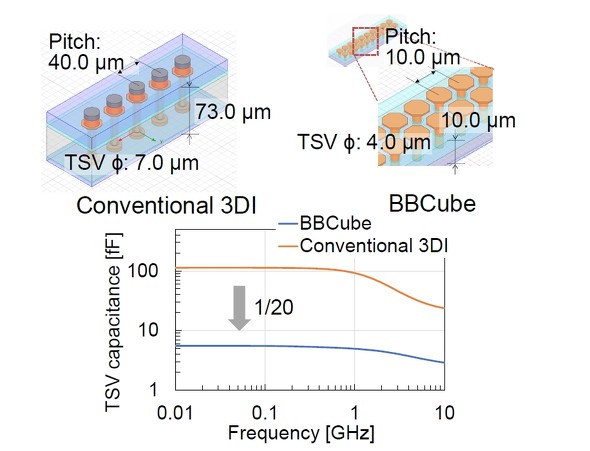

研究グループは、3次元電磁界解析を用い、BBCubeのTSVにおける寄生容量を算出した。このデータから、3次元実装した従来のTSVと比べ16倍の密度を実現しつつ、配線の寄生容量は20分の1になることが分かった。しかも、CPU/GPUとメモリ間は1万6000本もの信号線で超並列に接続できるという。

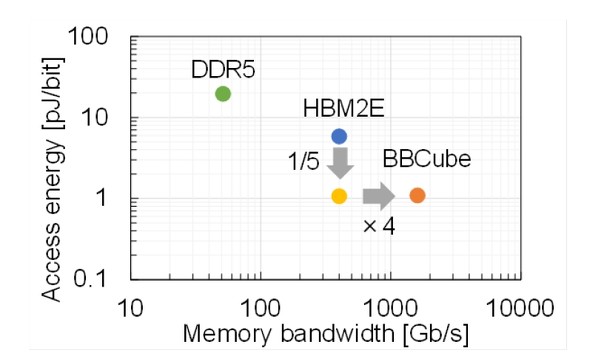

CPU/GPUとメモリ間のデータ伝送におけるエネルギーも解析した。この結果、BBCube3DはPC/サーバ用メモリ(DDR5)と比べ13倍、AIなどに用いる広帯域メモリ(HBM2E)に比べ4倍という帯域幅でデータ伝送を実現しながら、電力消費はDDR5の20分の1、HBM2Eの5分の1に抑えることができるという。

研究グループは今後、CPU/GPUとメモリをバンプレスWOWとCOWプロセスで積層したBBCube 3Dを試作し、「大容量データ伝送と低消費電力の両立」について実証していく。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

東工大ら、高伝導率のリチウムイオン伝導体を開発

東工大ら、高伝導率のリチウムイオン伝導体を開発

東京工業大学と高エネルギー加速器研究機構、東京大学の研究グループは、伝導率が32mS cm-1という固体電解質のリチウムイオン伝導体を開発した。この材料を用い厚膜が1mmの正極を作製したところ、電極面積当たりの容量が現行の1.8倍となった。 “大学城下町“構想で「企業は大学を活用して」

“大学城下町“構想で「企業は大学を活用して」

東京工業大学の副学長で産学官連携担当を務める大嶋洋一氏が、OMDIA主催のイベントで講演を行った。半導体業界の研究開発において大学のポテンシャルが十分に活用されていないことを指摘し、大学と企業が集い技術を発展させる「大学城下町」の構想など、産学連携のさらなる可能性について語った。 300GHz帯でビームフォーミングに成功、6G見据え

300GHz帯でビームフォーミングに成功、6G見据え

NTTと東工大は、ビームフォーミングを用いた300GHz帯高速無線データ伝送に成功したと発表した。移動する受信端末に向かって超大容量データを瞬時に転送できるようになるといい、第6世代移動通信(6G)への活用が期待される。 6G向けサブテラヘルツ帯フェーズドアレイ無線機IC

6G向けサブテラヘルツ帯フェーズドアレイ無線機IC

東京工業大学は、6G(第6世代移動通信)に向けて、サブテラヘルツ帯で全二重通信を可能とする「フェーズドアレイ無線機IC」を開発した。モバイル端末やIoT機器などへの搭載を視野に入れている。 東工大ら、PIM型NNアクセラレーターのマクロを開発

東工大ら、PIM型NNアクセラレーターのマクロを開発

東京工業大学と工学院は、モバイルエッジデバイスに搭載可能な、PIM(プロセッシングインメモリ)型ニューラルネットワーク(NN)アクセラレーターのマクロを開発した。動作時と待機時の電力消費が極めて小さく、高い演算能力とエネルギー効率を実現できるという。 最高の酸化物イオン伝導度を示す酸塩化物を発見

最高の酸化物イオン伝導度を示す酸塩化物を発見

東京工業大学は、200℃以下の低温域で酸化物イオン伝導度が最高値となる、新たな「酸塩化物」を発見した。その結晶構造とイオン拡散経路、酸化物イオン伝導度のメカニズムも解明した。

![バンプレスWOWとCOWの断面写真[クリックで拡大] 出所:東京工業大学](https://image.itmedia.co.jp/ee/articles/2307/19/tm_230719titech02a.jpg)