エッジ向け「Spartan UltraScale+」、AMDが発表:コスト効率や電力効率を向上

AMDは、コスト効率や電力効率を高めるなど、エッジ向けに最適化したFPGAファミリー「AMD Spartan UltraScale+」を発表した。

「業界最高水準」のI/O対ロジックセル比率を実現

AMDは2024年3月、コスト効率や電力効率を高めるなど、エッジ向けに最適化したFPGAファミリー「AMD Spartan UltraScale+」を発表した。

Spartan UltraScale+は、16nm FinFET技術を用いるとともに、ハード化されたLPDDR5メモリコントローラやPCIe Gen4×8などを採用することによって、28nm Artix 7ファミリーと比べ、消費電力を30%削減した。

同ファミリーとしては、ロジックセル数が11K個で最大I/O数が304本の「SU10P」から、ロジックセル数が218K個で最大I/O数が572本の「SU200P」まで、9製品を用意した。I/O数が多いため、複数のデバイスやシステムとシームレスに統合し、効率の良い接続が可能となる。

「28nm以下のプロセス技術で製造されたFPGAとしては、業界最高水準のI/O対ロジックセル比率を実現した」(同社)という。パッケージの外形寸法はSU10Pなどの10×10mm品から、SU200Pなどの23×23mm品まで、3タイプを用意した。

セキュリティについても最新の機能をサポートしている。IP保護に向けたNIST認定アルゴリズムによるポスト量子暗号のサポートや、PPK/SPKキーなどによる改ざん防止、SEU(シングルイベントアップセット)性能の強化による信頼性向上、などである。

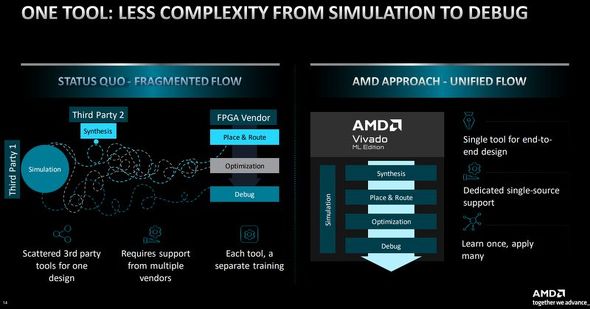

FPGA市場におけるAMDの強みは、提供する開発環境にもある。「AMD Vivado Design Suite」や「Vitis Unified Software Platform」を活用すれば、1つのツールでシミュレーションからデバッグまで一貫して行える。このため、設計者は開発効率を高めることができる。

なお、Spartan UltraScale+のサンプル品と評価キットは、2025年前半より提供を始める。ツールのサポートは2024年第4四半期の予定。仕様書は既に公開している。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

AMDの新GPUは、NVIDIA H100に比肩しうるか?

AMDの新GPUは、NVIDIA H100に比肩しうるか?

AMDは2023年6月、NVIDIAのフラグシップGPU「H100」に対抗する製品として、生成AI向けの高性能GPU「MI300X」を発表した。「AIは最大かつ最も戦略的な成長機会」とするAMDだが、新製品によって、市場を先行するNVIDIAに迫ることができるだろうか。 ADASの機能をFPGAレベルで瞬時に切り替え、AMDがデモ

ADASの機能をFPGAレベルで瞬時に切り替え、AMDがデモ

AMDザイリンクスは「第15回 オートモーティブワールド」で、周辺監視とDMS(ドライバーモニタリングシステム)の2つの機能を、FPGAレベルで瞬時に切り替えるデモを披露した。 旧Altera部門の新社名は「Altera」、Intelが発表

旧Altera部門の新社名は「Altera」、Intelが発表

Intelは、同社から分離したFPGAを手掛けるプログラマブル・ソリューション・グループ(PSG)事業(旧Altera部門)の社名をAlteraに決定したと発表した。今後2〜3年以内のIPOを目指している。 ラティス、ミッドレンジFPGA製品に2種類を追加

ラティス、ミッドレンジFPGA製品に2種類を追加

ラティスセミコンダクターは、ミッドレンジのFPGA製品ファミリーとして、「Lattice Avant-G」と「Lattice Avant-X」の2種類を発表した。通信機器やコンピューティング、産業機器、車載機器などの用途に向けた製品である。 ラティス、車載向けソリューションスタックを発表

ラティス、車載向けソリューションスタックを発表

ラティスセミコンダクターは、FPGA「Nexus」や「Avant」を用いた車載システムの開発を支援する「Lattice Driveソリューションスタック」を発表した。その第1弾は「インフォテインメントディスプレイのブリッジングと処理」に向けたソリューションとなる。 XilinxはロボットとFAに注力、TSNと5Gの接続技術も

XilinxはロボットとFAに注力、TSNと5Gの接続技術も

2022年2月14日(米国時間)、AMDがXilinxの買収を完了した。XilinxはAMDの「Adaptive Embedded Computing Group(AECG)」となり、FPGAなどのプログラマブルデバイスを引き続き手掛ける。XilinxのCEOであったVictor Peng氏は、AECGのプレジデントとなる。