表面実装型電子部品(SMD部品)の小型化トレンド:福田昭のデバイス通信(448) 2022年度版実装技術ロードマップ(72)(2/2 ページ)

JEITA「2022年度版 実装技術ロードマップ」を解説するシリーズ。今回から、第4章「電子部品」の概要を説明していく。

積層セラミックコンデンサーは「0603」サイズの時代が続く

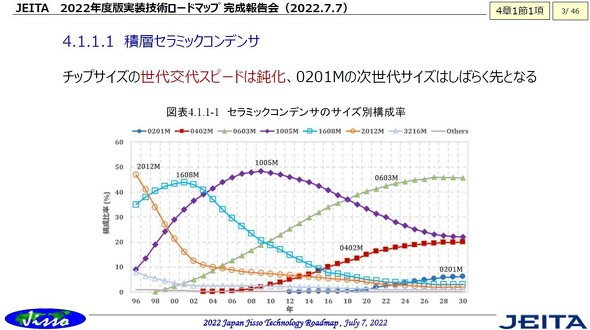

表面実装型積層セラミックコンデンサー(MLCC)のチップサイズは、1990年代の「2012M」(2.0mm×1.25mm、Mは単位がメートル法であることを示す)から2000年代前半の「1608M」(1.6mm×0.8mm)、2000年代後半〜2010年代前半の「1005M」(1.0mm×0.5mm)と主流(構成比率が最も高いサイズ)のサイズが小さくなってきた。

2010年代末〜2020年代はさらに小さな「0603M」(0.6mm×0.3mm)サイズが主流となり、構成比率をゆっくりとだが高めていく。次世代品とされる「0402M」(0.4mm×0.2mm)は2010年代と2020年代と通じて構成比率を漸増させるものの、2030年でも構成比率は20%とそれほど高くはない。2030年も主役は「0603M」サイズで、構成比率は45%に達すると予測する。2010年に50%近い比率を占めた「1005M」サイズは、2010年代と2020年代と通じて比率を下げていく。それでも2030年の比率は20%強とサイズ別では第2位に付ける。

表面実装型抵抗器の小型化はコンデンサーよりも緩やか

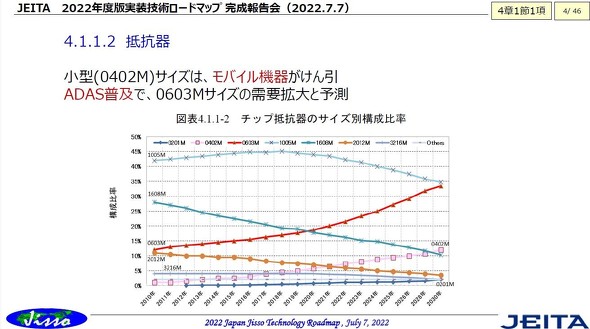

表面実装型抵抗器(チップ抵抗器)の小型化は積層セラミックコンデンサーに比べると緩やかだ。2010年代と2020年代は「1005M」サイズが最大比率を占め続ける。スマートフォンのローエンドモデルとミドルレンジモデルは「0603M」サイズを数多く採用しており、同サイズの比率は2020年代を通じて上昇する。2030年には「1005M」サイズと「0603M」サイズの構成比率が拮抗する。

スマートフォンのハイエンドモデルは、さらに小さな「0402M」サイズのチップ抵抗器を多用している。それでも同サイズの構成比率はあまり増えない。2020年に5%強、2030年に10%強と推定する。

小型化と薄型化が進行する表面実装型EMC対策部品

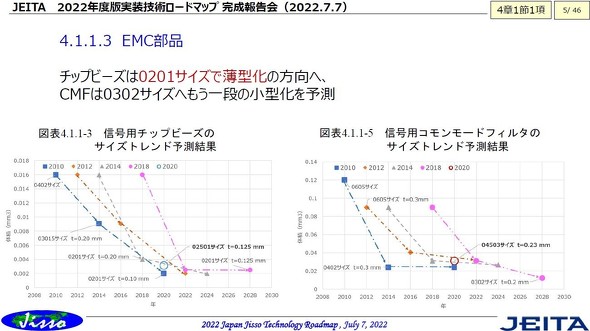

表面実装型EMC対策部品のサイズは、過去に発行した「実装技術ロードマップ」で予測した小型化トレンドと2020年時点で販売されている部品のサイズを比較するとともに、将来を予測した。対策部品としては信号用チップビーズと信号用コモンモードフィルター(CMF)を選んだ。

信号用チップビーズの最小寸法は2010年の「0402」サイズから2020年には「02501M」(0.25mm×0.1mm)サイズへと小型化が進んだ。厚みは「0402M」部品の0.2mmから「02501M」部品の0.125mmへと低下した。今後は「0201M」(0.2mm×0.125mm前後)サイズの開発が進むと予測した。

信号用コモンモードフィルター(CMF)の最小寸法は、2010年の「0605M」(0.65mm×0.5mm、0.68mm×0.55mmなど、定格電流100mA)サイズから、2020年には「0402M」サイズへと小さくなると過去のロードマップでは予測した。2021年には「04503M」(0.45mm×0.3mm、定格電流50mA)サイズのCMFが発売されたことで、ほぼロードマップの予測通りに小型化が実現した。今後は、さらに小型化した「0302M」(0.3mm×0.2mm前後)サイズの登場を予想している。

表面実装型EMC対策部品のチップサイズ予測推移。左は信号用チップビーズ、右は信号用コモンモードフィルター(CMF)。なおグラフの縦軸は体積[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

プロセッサやメモリなどの進化を支えるパッケージ基板

プロセッサやメモリなどの進化を支えるパッケージ基板

今回は第3章第4節第8項(3.4.8)「パッケージ基板」の概要を説明する。パッケージ基板の変遷と、パッケージ基板に対する要求仕様のロードマップを解説する。 プリント基板の「弁当箱」からパッケージとチップまで、電磁シールド技術が進化

プリント基板の「弁当箱」からパッケージとチップまで、電磁シールド技術が進化

JEITA「2022年度版 実装技術ロードマップ」の「パッケージ組立プロセス技術動向」について解説するシリーズ。今回は第3章第4節第6項(3.4.6)「電磁シールド」の概要を説明する。 シリコンダイを光や熱、ホコリ、機械衝撃などから保護する樹脂封止技術

シリコンダイを光や熱、ホコリ、機械衝撃などから保護する樹脂封止技術

今回は第3章第4節第5項(3.4.5)「樹脂封止技術(アンダーフィル、モールディング)」の概要を説明する。 ダイボンディングと電極ボンディングで半導体チップを外部とつなぐ

ダイボンディングと電極ボンディングで半導体チップを外部とつなぐ

今回は、第3章第4節第4項(3.4.4)「ダイボンディングおよび電極ボンディング技術」の概要を説明する。 回路形成済みウエハーの裏面研削とダイシング

回路形成済みウエハーの裏面研削とダイシング

今回は第3章第4節第3項(3.4.3)「ウエハ(チップ)薄型化技術とウエハハンドリング」の概要を説明する。第3項は、裏面研磨技術、ウエハーダイシング技術、DBG(Dicing Before Grinding)プロセスの3つで構成される。 半導体チップの高密度3次元積層を加速するハイブリッド接合

半導体チップの高密度3次元積層を加速するハイブリッド接合

今回から、第3章第4節(3.4)「パッケージ組立プロセス技術動向」の内容を紹介する。本稿では、ハイブリッドボンディングを解説する。