チップ抵抗器の小型化が過度な温度上昇を招く(前編):福田昭のデバイス通信(451) 2022年度版実装技術ロードマップ(75)

今回から、第4章第1節第3項「部品実装・設計時の注意点」の概要を説明していく。この項は、「熱設計」「電気性能」などの4つのパートで構成される。

表面実装部品の実装・設計時の注意点を解説

電子情報技術産業協会(JEITA)が3年ぶりに実装技術ロードマップを更新し、「2022年度版 実装技術ロードマップ」(書籍)を2022年7月に発行した。本コラムではロードマップの策定を担当したJEITA Jisso技術ロードマップ専門委員会の協力を得て、ロードマップの概要を本コラムの第377回からシリーズで紹介している。

第448回から、第4章「電子部品」の概要説明を始めた。前々回と前回は、表面実装型電子部品(SMD)の中でインダクターと積層セラミックコンデンサー、チップ抵抗器の製品開発動向を前後編で述べた。第4章第1節第2項「技術動向」に相当する部分である。

今回からは、第4章第1節第3項「部品実装・設計時の注意点」の概要説明を始める。この項は「4.1.3.1 熱設計」「4.1.3.2 電気性能」「4.1.3.3 信頼性」「4.1.3.4 実装」の4つのパートで構成される。

最初のパートである第4章第1節第3項第1目「4.1.3.1 熱設計」では、チップ抵抗器を事例として取り上げ、熱設計の現状と対策を説明している。具体的には、「(1)チップ抵抗器の小型化・高電力化と熱問題」「(2)チップ抵抗器の温度上昇と基板放熱の関係」「(3)基板放熱に適した新たな温度基準と取組み」の3つの項目がある。

定格電力より低い電力でも実装条件によってはトラブルが発生

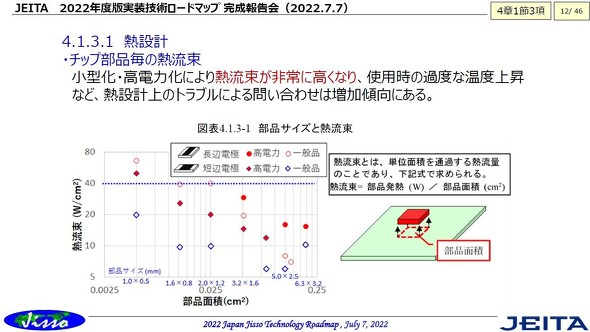

前回で述べたように、チップ抵抗器は小型化と定格電力拡大を並行して進めてきた。例えば「2012M」タイプのチップ抵抗器の定格電力は2000年頃まで0.100Wだったのが、2002年以降は0.125Wに増加し、2016年以降は0.250Wに急拡大した(ロードマップ書籍本体458ページの図表4.1.2-14を参照)。単位面積当たりの熱流量(「熱流束」と呼ぶ)は当初の10W/cm2から、現在では40W/cm2にまで上昇した。

この結果、電子回路基板の動作時にチップ抵抗の温度が過度に上昇するといったトラブルが増加しているとロードマップは指摘する。単純に放熱性能が同じままだと想定すると、定格電力が2倍になると温度上昇も2倍になる可能性がある。

従来、チップ抵抗は、周囲温度が定格値(70℃)よりも高い条件では、定格電力よりも低い負荷電力で使用することが求められてきた。70℃の負荷電力(定格電力)を100%とすると、120℃では定格電力の40%に負荷を下げなければならない。ただしこの考え方は表面積の大きなリード付き抵抗器が主体であった時代のもので、表面実装タイプの抵抗器では適切とは限らない。

このため実装形態によっては定格電力の半分に満たない電力条件でも、温度の著しい上昇が発生することがある。詳しくは後編で述べたい。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

表面実装型電子部品(SMD部品)の開発動向(後編)

表面実装型電子部品(SMD部品)の開発動向(後編)

後編となる今回は、「セラミックコンデンサの高容量化・低ESR化、薄型化」や「チップ抵抗器の高電力化」について解説する。 プロセッサやメモリなどの進化を支えるパッケージ基板

プロセッサやメモリなどの進化を支えるパッケージ基板

今回は第3章第4節第8項(3.4.8)「パッケージ基板」の概要を説明する。パッケージ基板の変遷と、パッケージ基板に対する要求仕様のロードマップを解説する。 表面実装型電子部品(SMD部品)の小型化トレンド

表面実装型電子部品(SMD部品)の小型化トレンド

JEITA「2022年度版 実装技術ロードマップ」を解説するシリーズ。今回から、第4章「電子部品」の概要を説明していく。 プリント基板の「弁当箱」からパッケージとチップまで、電磁シールド技術が進化

プリント基板の「弁当箱」からパッケージとチップまで、電磁シールド技術が進化

JEITA「2022年度版 実装技術ロードマップ」の「パッケージ組立プロセス技術動向」について解説するシリーズ。今回は第3章第4節第6項(3.4.6)「電磁シールド」の概要を説明する。 シリコンダイを光や熱、ホコリ、機械衝撃などから保護する樹脂封止技術

シリコンダイを光や熱、ホコリ、機械衝撃などから保護する樹脂封止技術

今回は第3章第4節第5項(3.4.5)「樹脂封止技術(アンダーフィル、モールディング)」の概要を説明する。 ダイボンディングと電極ボンディングで半導体チップを外部とつなぐ

ダイボンディングと電極ボンディングで半導体チップを外部とつなぐ

今回は、第3章第4節第4項(3.4.4)「ダイボンディングおよび電極ボンディング技術」の概要を説明する。