中国勢の限界見えた? 主要スマホ向けプロセッサの競争環境:Yoleが調査(2/2 ページ)

フランスの市場調査会社Yole Groupは、フラグシップスマートフォン用のアプリケーションプロセッサを調査し、「APU - Smartphone SoC Floorplan Comparison 2024(APU - スマートフォン向けSoCのフロアプラン比較 2024)」と題する研究の分析概要を発表した。【訂正あり】

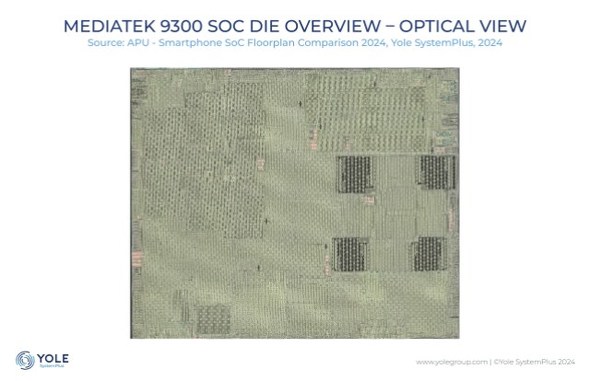

MediaTekは4nmノードでもダイサイズは最大規模

最先端リソグラフィやさまざまなファウンドリーツールに対する制裁措置が中国に最初に課されて以来、「SMICのような中国国内のファブやHiSiliconのような設計メーカーは、革新的な競争方法を見つけるのではないか」と推測されてきた。HiSiliconのKirin 9000は、同社がTSMCの高度技術から追いやられて以来初めての主要なチップ設計であるため、Yole Groupの調査は興味深いタイミングで行われたといえる。

SMICは、7nmノードでKirin 9000を製造する。これはTSMCがApple向けに適用する3nmや、Samsungが自社製およびGoogle製プロセッサ向けに、TSMCがQualcomm/MediaTek向けに適用する4nmよりも後進的な技術だ。HiSiliconの設計が最大規模のチップになったのはこのためだといえるだろう。しかし、MediaTekのプロセッサは、はるかに高度なTSMCの4nmプラットフォームで構築されているにもかかわらず、ダイサイズは最大規模だ。TSMCの4nmプロセスは、トランジスタ密度を向上させたが、MediaTekの設計では超大型のArm X4コアを4個搭載するため、Si(シリコン)を広範に使用する必要があるのだ。

Dimensity 9300のダイサイズについて少し詳しく説明しよう。これは、GoogleやQualcomm、Samsungのダイに比べてやや大きいだけだ。これら3社はいずれもオンチップモデムを搭載しているため、MediaTekの設計は、機能的にはQualcommとSamsungと同等だといえる。Googleの設計戦略は、モデム機能を除外しても最大規模のダイサイズのグループに含まれる。これは、AppleがApple A17の設計サイズをかなり縮小する戦略をとったためだ。

HiSiliconのチップは、グループの中では最小で、Apple A17よりも数平方ミリメートル小さい。Kirin 9000はモデムを搭載しているが、Appleは搭載しておらず、Googleダイも比較的大型でモデムを搭載していないということを考えると、ますます混乱するのではないだろうか。

AppleとHiSiliconは、一方が最先端の技術で製造され、もう一方はそれよりも遅れた世代で製造されているという事実を考慮すると、さらに相違点が顕著になる。Kirinにモデムブロックが搭載されていることについては、繰り返し述べるだけの価値がある。

米国の技術制裁措置で中国に製造制限が課されたことにより、HiSiliconはフロアプランに統合モデムを搭載しながら合理的なチップサイズを維持する上で、設計を変更せざるを得なくなった。Kirin 9000は、モデム用の領域を確保するためにいくつかの点で妥協している。Kirin 9000はさまざまな計算ベンチマークで後れを取っているため、同等グループの他の製品のベンチマークをいくつか見れば、その詳細を説明できるだろう。実際に、いくつかの性能/消費電力ベンチマークはその前世代製品よりも劣っている。

Kirin 9000は、CPU、GPU、NPU、システムSRAMなど、全ての主要な計算ブロックの面積を削減するため、ダイサイズは最小になる。ただし、トランジスタ数の推定値を考慮すると、限界は明らかだ。グループ内で最も先進的なプロセスを採用したApple A17には、Kirinチップの約2倍のトランジスタが含まれている。

HiSilicon Kirin 9000は、遅れを取っている中国のファウンドリーで製造されているにもかかわらず、最小サイズだ。ダイサイズの対極にあるMediaTek Dimensity 9300は、4つのArm Cortex-X4コアを搭載し、強力なパワーを発揮する。これらのトップクラスのスマートフォンプロセッサの設計を比較すると、チップの分割と配置のトレードオフだけでなく、多くの紆余曲折があることが分かる。

【訂正:2024年11月7日12時25分 当初、「HiSilicon Kirin 9000は、中国国内の最先端のファウンドリーで製造されているにもかかわらず、最小サイズだ。」としておりましたが、「HiSilicon Kirin 9000は、遅れを取っている中国のファウンドリーで製造されているにもかかわらず、最小サイズだ。」の誤りです。お詫びして訂正致します。】

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「iPhone 16」を分解 Appleの細やかな半導体設計

「iPhone 16」を分解 Appleの細やかな半導体設計

2024年9月に発売されたApple「iPhone 16」「iPhone 16 Pro」を分解した。前世代の「iPhone 15」シリーズに比べて、内部構造なども大きく変化している。分解結果からは、Appleが同じiPhone 16シリーズでも、主要コンポーネントを一つ一つ最適化していることが伺えた。 CHIPS法の成功事例となるか パワー半導体ファウンドリーを目指すPolar

CHIPS法の成功事例となるか パワー半導体ファウンドリーを目指すPolar

米CHIPS法による助成金を最初に獲得した企業で、サンケン電気の米国子会社でもあるPolar Semiconductorは、より幅広い顧客向けにパワー半導体を製造する商業ファンドリーへと転換しようとしている。半導体製造の自国回帰を進める米国にとって、Polarの戦略が成功するか否かは重要な指標になりそうだ。 チップレットベースのデータセンターAI製品に注力、韓国新興

チップレットベースのデータセンターAI製品に注力、韓国新興

韓国のAI(人工知能)チップ新興企業Rebellionsは、チップレットベースのデータセンター用AIアクセラレーターの開発と展開に力を入れている。2020年に設立された同社はさまざまな企業と協業しながら、韓国で存在感を高めている。 熱いスマホを冷やす アクティブ冷却用半導体チップ

熱いスマホを冷やす アクティブ冷却用半導体チップ

米xMEMSが開発した冷却用半導体チップにより、スマートフォンなどの小型、薄型デバイスでアクティブ冷却機能を実現できるかもしれない。同社は、MEMSスピーカー向けで培った技術を活用して、冷却用半導体チップを開発した。 「iPhone」分解 15 Pro Maxまで10世代分を一挙公開

「iPhone」分解 15 Pro Maxまで10世代分を一挙公開

「EE Times Japan」に掲載した主要な記事を、読みやすいPDF形式の電子ブックレットに再編集した「エンジニア電子ブックレット」。今回は、2007年に誕生した「iPhone」の歴史を振り返るとともに、2014年発売の「iPhone 6」から2023年発売の「iPhone 15 Pro Max」まで、10世代の解剖記事をまとめました。 スマホの2台に1台に採用されている「CSP MOSFET」を展示、ヌヴォトン

スマホの2台に1台に採用されている「CSP MOSFET」を展示、ヌヴォトン

ヌヴォトン テクノロジージャパンは、「人とくるまのテクノロジー展 2024 YOKOHAMA」(2024年5月22〜24日/パシフィコ横浜)に出展し、小型化と低オン抵抗を両立したCSP(Chip Size Package) MOSFETを展示した。