ニュース

3次元実装の半導体に対応するフラックス洗浄装置、リックス:数十マイクロメートルの隙間も確実に

リックスは、AI向け半導体などで採用が進む2.5/3次元実装技術に対応した「フラックス洗浄装置」を開発したと発表した。極めて狭い隙間にあるフラックス残渣を確実に洗浄できる機構について特許を出願中だ。

フラックス洗浄液を充填させる減圧機構を開発、特許も申請中

リックスは2025年10月、AI向け半導体などで採用が進む2.5/3次元実装技術に対応した「フラックス洗浄装置」を開発したと発表した。極めて狭い隙間にあるフラックス残渣を確実に洗浄できる機構について特許も出願中だ。

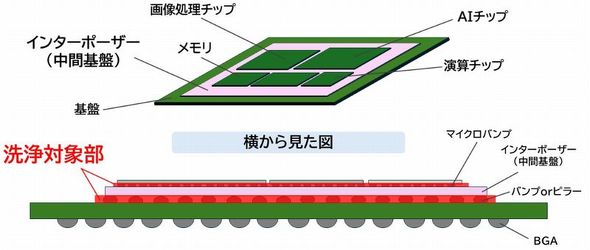

AI向けなどの先端半導体デバイスでは、複数の小さい半導体チップを組み合わせ、これらを接続するためにインターポーザと呼ばれる中間基板上に実装して1つのパッケージに集積する技術が注目されている。ところが従来方法だと、半導体チップとインターポーザ、あるいはインターポーザとパッケージ基板の間にできる極めて狭い隙間の洗浄が難しかったという。

そこでリックスは、狭い隙間でもフラックス洗浄剤を充填させることができる減圧機構を開発し採用した。これにより、数十マイクロメートルという狭い隙間であっても、フラックス残渣を取り除くことが可能となった。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

最先端ロジック/メモリ用半導体製造装置、AMATが3製品発表

最先端ロジック/メモリ用半導体製造装置、AMATが3製品発表

アプライド マテリアルズ(AMAT)は、最先端ロジックや高性能メモリチップ、高度なパッケージング技術に対応する半導体製造装置として、ボンディング装置など3製品を発表した。 名古屋大ら、溶液成長法による6インチp型SiCウエハー試作に成功

名古屋大ら、溶液成長法による6インチp型SiCウエハー試作に成功

オキサイドパワークリスタルとMipox、UJ-Crystal、アイクリスタル、産業技術総合研究所(産総研)および名古屋大学の開発グループが、溶液成長法とシミュレーション技術を活用し、6インチp型炭化ケイ素(SiC)ウエハーおよび、6インチ/8インチn型SiCウエハーの試作に成功した。 チップレット集積の歩留まり向上へ 高速なオーバーレイ測定を実現

チップレット集積の歩留まり向上へ 高速なオーバーレイ測定を実現

EV Group(EVG)は、300mmウエハー上で100%のダイオーバーレイ測定を、従来に比べ最大15倍というスループットで行えるダイツーウエハー(D2W)オーバーレイ計測プラットフォーム「EVG40 D2W」を発表した。 GaNで半導体製造の欠陥検出 キオクシア岩手で検証へ

GaNで半導体製造の欠陥検出 キオクシア岩手で検証へ

名古屋大学発スタートアップのPhoto electron Soul(PeS)と名古屋大学の天野・本田研究室は、共同開発したGaN系半導体フォトカソード技術を用いた検査・計測システムをキオクシア岩手に導入し、半導体デバイス製造工程での欠陥検出などについて評価を行うと発表した。 「内部が空洞」のマイクロバンプで低温接合、新たな半導体実装技術

「内部が空洞」のマイクロバンプで低温接合、新たな半導体実装技術

東北大学の研究グループは産業技術総合研究所(産総研)と共同で、表面活性化接合とテンプレートストリッピングの技術を組み合わせて、中空ピラミッド構造のマイクロバンプを作製し、異種材料を低温で強固に接合できる半導体実装技術を開発した。 極薄の先端半導体チップを高スループットで実装、生産効率10倍

極薄の先端半導体チップを高スループットで実装、生産効率10倍

東レエンジニアリングは、レーザー転写技術を応用して、極薄の半導体チップを高いスループットで実装できる技術を開発した。次世代の情報通信システムなどに用いられる先端半導体チップの実装工程で、生産効率を従来の10倍以上に高めることが可能になるという。