ニュース

Rapidus、千歳で製造した2nm GAAトランジスタの試作品を初展示:SEMICON Japan 2025(2/2 ページ)

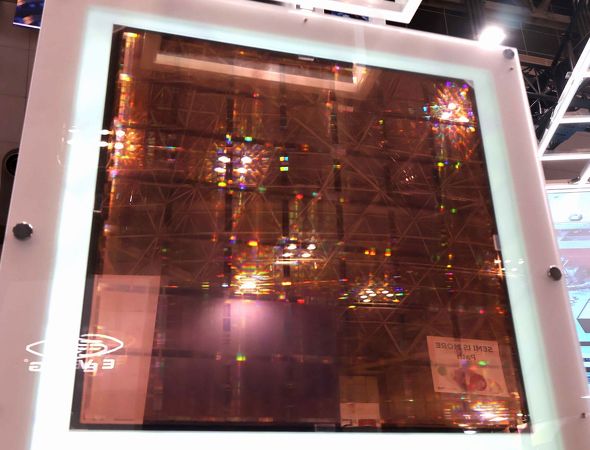

Rapidusは「SEMICON Japan 2025」(2025年12月17〜19日)に出展し、北海道千歳市の開発/製造拠点「IIM(イーム)」で製造した2nm GAA(Gate All Around)トランジスタや600mm角 再配線層(RDL)インターポーザーパネルの試作品を展示した。

60mm角RDLインターポーザーパネルの試作品も展示

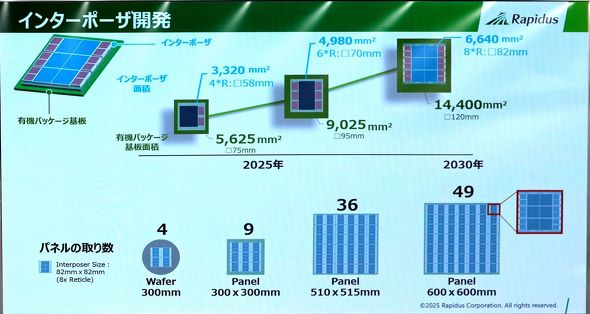

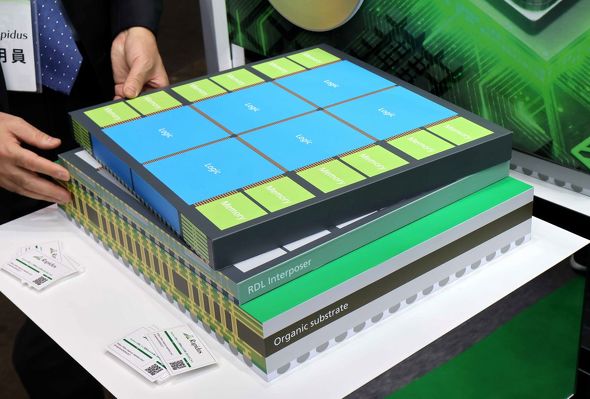

後工程では、チップレットパッケージに用いるRDLインターポーザーの開発を行っている。82mm角のインターポーザーの取り数は、300mmウエハーでは4枚だが、600mm角パネルでは49枚と、10倍以上に増加する。そのため、Rapidusは600mm角のRDLインターポーザーパネルの開発を行っていて、ブースではその試作品の実物や、チップレットパッケージの構造模型などを展示した。

RDLインターポーザーの製造においては、ガラスキャリア上に配線を形成し、必要に応じて微細配線用のチップであるブリッジチップを埋め込んだ後、上層配線を形成する。その後、上層と下層を接合するためのピラー形成、ブリッジチップ搭載、樹脂封止、研磨、配線層形成、パッド形成を行い完成となる。その後さらに、RDLインターポーザーにロジックやメモリを搭載後、ガラスキャリアを剥がして有機基板に接続し、モールドで封止して、RDLインターポーザーのチップ実装工程は完了だ。

Rapidusは、2027年に前工程の、2027年後半〜2028年前半に後工程の量産開始を目指す。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Rapidus、600mm角インターポーザーパネルを初披露 NVIDIAの受託にも意欲

Rapidus、600mm角インターポーザーパネルを初披露 NVIDIAの受託にも意欲

Rapidus 社長兼CEOの小池淳義氏は「SEMICON Japan 2025」内のセミナープログラムに登壇。同社が掲げるビジネスモデル「RUMS(Rapid and Unified Manufacturing Service)」や前工程/後工程の最新の取り組みを紹介したほか、600mm角の再配線層(RDL)インターポーザーパネルの試作品を披露した。 AIで半導体設計時間を半減 Rapidusの2nm向け支援ツール

AIで半導体設計時間を半減 Rapidusの2nm向け支援ツール

Rapidusは2025年12月17日、同社2nm製造プロセス向けの半導体設計支援ツール群「Raads」を発表した。2026年から順次リリース予定で、設計期間の50%短縮と、設計コストの30%削減が可能だとしている。 Rapidusは31年度に上場目指す、27年度後半に2nm世代量産

Rapidusは31年度に上場目指す、27年度後半に2nm世代量産

赤沢亮正経済産業大臣は2025年11月21日、政府がRapidusに対して1000億円を出資する考えを発表した。また、この日公開されたRapidusの実施計画では、同社が2031年度頃に株式上場を目指す方針などが明らかになった。 ついにできた!Rapidus試作ライン稼働、2nm GAAトランジスタの動作を確認

ついにできた!Rapidus試作ライン稼働、2nm GAAトランジスタの動作を確認

Rapidusは、最先端半導体の開発/生産を行う「IIM-1」(北海道千歳市)で、2nm GAA(Gate All Around)トランジスタの試作を開始し、動作を確認したと発表した。Rapidus 社長兼CEOの小池淳義氏は「2nm GAAトランジスタがこのスピードで本当にできたということに、顧客は非常に驚き、ものすごい期待を持つだろう」と語った。 「Rapidusを支援したい」 VCに転身のPat Gelsinger氏、日米の協業に意欲

「Rapidusを支援したい」 VCに転身のPat Gelsinger氏、日米の協業に意欲

米国を拠点にディープテックへの投資を行うベンチャーキャピタルのPlayground Globalは、メディア向けの事業説明会を開催した。説明会にはPlayground ゼネラルパートナー兼共同創業者のPeter Barrett氏、Intelの前CEOで現在Playgroundのゼネラルパートナーを務めるPat Gelsinger氏らが登壇した。