不揮発性パワーゲーティング、メニーコアプロセッサの待機電力削減に威力:新技術(2/2 ページ)

東京工業大学(東工大)像情報工学研究所の菅原聡准教授らの研究グループと神奈川科学技術アカデミー(KAST)は、不揮発性パワーゲーティング(NVPG)がメニーコアのプロセッサやSoCの待機時電力削減に極めて有効なアーキテクチャであることを実証した。

ストアフリーシャットダウンでさらに

これらの回路構成とアーキテクチャを用い、回路シミュレーションを行った。このシミュレーションでは、CMOSデバイスにはFinFETの「Predictive Technology Model」を、MTJには同研究グループが開発した高精度のマクロモデルをそれぞれ採用した。

NVPGは、通常のSRAM動作とMTJへ書き込む不揮発記憶の動作を分離することができることから、NVPGにおける通常の読み出しと書き込みは、SRAMと同じ速度で実行することができる。これに対して、NOFは常に不揮発記憶の動作を行う。このため、本来なら不揮発記憶が不要な通常の書き込み時には動作速度が低下する。余分な動作を行うため、電力消費も増えることになる。

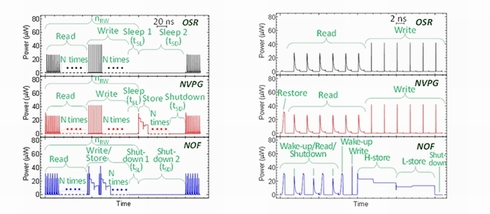

NVPGとNOFによるNV-SRAMとSRAMの動作波形。左図はベンチマークシーケンスに従って動作させた時の波形。右図はそれを拡大したもの (クリックで拡大) 出典:東京工業大学、神奈川科学技術アカデミー

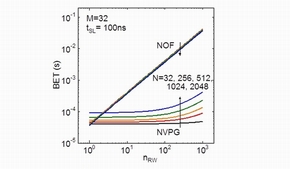

NOFでは頻繁に電源遮断を行うことで、消費電力を節減できるという主張もあるが、今回の研究からはこのような依存性は見いだせなかったとしている。電源遮断によってエネルギーを削減できる最低の電源遮断時間BET(Break-even Time)と読み出し/書き込み動作サイクル数の依存性についても検証した。NOFでは読み出し/書き込み動作サイクル数の増加により、BETが大きく増加した。不揮発記憶と電源遮断を繰り返すことで、エネルギー削減効果が小さくなる。一方、NVPGも読み出し/書き込み動作サイクル数には依存するが、その影響は小さく、読み出し/書き込み動作サイクル数の増加に伴うBETの増大は、NOFに比べて極めて小さいことが分かった。さらに、同研究グループが提唱している「ストアフリーシャットダウン」を導入することで、BETをさらに削減できるという。ストアフリーシャットダウンとは、「書き込み済みのデータと同じデータは書き込まない」という不揮発記憶のアーキテクチャである。

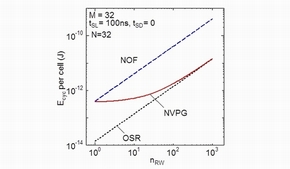

左図は消費エネルギーと読み出し/書き込み動作サイクル数との依存性を示したグラフ。NVPGの消費エネルギーは読み出し/書き込み動作サイクル数が増加すると通常のSRAMに漸近する。NOFではこうした効果は得られないことが分かった。右図はBETと読み出し/書き込み動作サイクル数の依存性を示したグラフである (クリックで拡大) 出典:東京工業大学、神奈川科学技術アカデミー

左図は消費エネルギーと読み出し/書き込み動作サイクル数との依存性を示したグラフ。NVPGの消費エネルギーは読み出し/書き込み動作サイクル数が増加すると通常のSRAMに漸近する。NOFではこうした効果は得られないことが分かった。右図はBETと読み出し/書き込み動作サイクル数の依存性を示したグラフである (クリックで拡大) 出典:東京工業大学、神奈川科学技術アカデミー今回の研究成果は、フランス・グルノーブルで開催された集積回路に関する国際学会「DATE」で、2015年3月11日に発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

TDKと東京工業大学、磁性・磁石技術の先端研究で組織的連携協定を締結

TDKと東京工業大学、磁性・磁石技術の先端研究で組織的連携協定を締結

TDKは、東京工業大学と磁性・磁石技術をベースとした先端技術の共同研究を進めていくために、組織的連携協定を結んだ。磁性・磁石技術応用の新たな可能性を追求していく。 目を超えたイメージセンサー、人間と同じ物体認識ができるステレオカメラ……“コンピュータビジョン”の可能性

目を超えたイメージセンサー、人間と同じ物体認識ができるステレオカメラ……“コンピュータビジョン”の可能性

ディジタルメディアプロフェッショナル(DMP)主催のセミナー「DMP Computer Visionセミナー2014」の基調講演に、ステレオカメラ「アイサイト」の開発者として知られる東京工業大学放射線総合センター准教授の実吉敬二氏が登壇した。本稿では、実吉氏らの講演を中心に、同セミナーの模様を紹介する。 省エネスパコン世界一の「TSUBAME-KFC」が連覇達成

省エネスパコン世界一の「TSUBAME-KFC」が連覇達成

東京工業大学は2014年7月、スーパーコンピュータの省エネランキング「The Green 500 List」の2014年6月版で、東工大が開発したスーパーコンピュータ「TSUBAME-KFC」が1位を獲得したと発表した。2013年11月版に続き、2期連続での首位獲得となった。 室温動作のテラヘルツ波検出器、カーボンナノチューブ用いて東工大らが開発

室温動作のテラヘルツ波検出器、カーボンナノチューブ用いて東工大らが開発

東京工業大学(東工大)量子ナノエレクトロニクス研究センターの河野行雄准教授らは、米国の大学や国立研究所と共同で、カーボンナノチューブを用いた室温動作のテラヘルツ波検出器を開発したと発表した。医療用の画像診断装置や空港のセキュリティ検査装置、食品用検査装置などへの応用が期待されている。 自動運転車はステレオカメラだけで実現できる――「アイサイト」開発者に聞く

自動運転車はステレオカメラだけで実現できる――「アイサイト」開発者に聞く

自動運転車などに不可欠な自動車の周辺環境を検知するセンサーとしてステレオカメラが注目を集めている。ステレオカメラの第1人者で、富士重工業のステレオカメラを使った運転支援システム「アイサイト(EyeSight)」の開発にも携わった東京工業大学放射線総合センター准教授の實吉敬二氏にステレオカメラの可能性などについて聞いた。