パッケージング技術がワンチップ化の限界を突破:福田昭のデバイス通信(102) TSMCが解説する最先端パッケージング技術(1)(2/2 ページ)

システムを複数のチップに分けてから高密度に集積化したパッケージは、SiP(System in Package)と呼ばれる。「ムーアの法則」を拡張するために、新しいSiP技術あるいはパッケージング技術が次々に登場している。今回から始まる新シリーズでは、こうした新しいパッケージング技術を紹介したい。

SoC(システムオンチップ)からSiP(システムインパッケージ)へ

システムをワンチップ化したシリコンは、システムLSIあるいはSoC(System on a Chip、呼称は「エスオーシー」)と呼ばれている。これに対してシステムを複数のチップに分けてから高密度に集積化したパッケージは、SiP(System in Package、呼称は「シップ」)と呼ばれることが少なくない。

最先端のパッケージング技術、あるいはSiP技術に求められるのは、外形寸法をワンチップと近い水準にまで小さくするとともに、消費電力を低減し、性能を高め、多くの機能を収容することである。

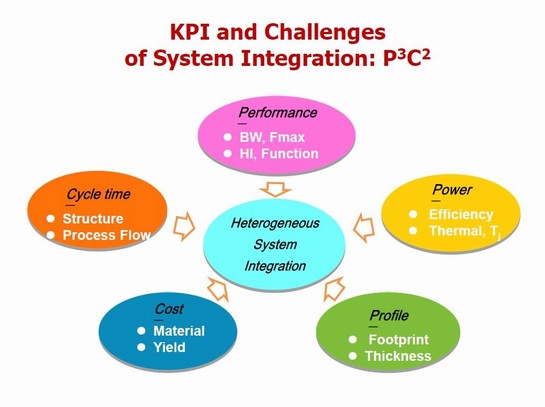

具体的には頭文字が「P」の3つの指標と、頭文字が「C」の2つの指標で与えられる。「Performance(性能)」「Power(消費電力)」「Profile(外形寸法)」、それから「Cycle time(開発期間)」「Cost(コスト)」である。

「Performance(性能)」は動作周波数やデータ転送速度(帯域幅)、機能などを指す。「Power(消費電力)」は消費電力そのもののほか、性能当たりの消費電力(電力効率)を意味する。「Profile(外形寸法)」は、プリント基板の占有面積と厚み(薄さ)のことである。

「Cycle time(開発期間)」はパッケージの構造と製造工程で決まる。「Cost(コスト)」は材料コストと生産歩留まりによって左右される。

(次回に続く)

⇒「福田昭のデバイス通信」バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

近代科学の創始者たちに、研究不正の疑いあり(コペルニクス編その1)

近代科学の創始者たちに、研究不正の疑いあり(コペルニクス編その1)

1510年ごろ、地動説のひな型となる論文「小論考(コメンタリオルス)」が生まれる。それを書いたのがコペルニクスだ。地動説の端緒となるコペルニクスの偉大さは疑いようもないことだが、その凄さを強調するあまりに現代では、いくつかの誤りが信じられている節がある。 「SEMICON West 2016」、imecが展望する5nm世代の配線技術(前編)

「SEMICON West 2016」、imecが展望する5nm世代の配線技術(前編)

imceによる、5nm世代のロジック配線プロセスを展望した講演を、前後編の2回にわたりお届けする。前半では、配線抵抗(R)、配線容量(C)、RC積という配線のパラメータの特徴を紹介する。さらに、10nm世代、7nm世代、5nm世代と微細化が進むと、配線抵抗(R)、配線容量(C)、RC積がどのように変化していくかを解説する。 中身が大変身した「iPhone 7」とその背景

中身が大変身した「iPhone 7」とその背景

2016年9月に発売されたAppleの新型スマートフォン「iPhone 7」。一部では、あまり目新しい新機能が搭載されておらず「新鮮味に欠ける」との評価を受けているが、分解して中身をみると、これまでのiPhoneから“大変身”を果たしているのだ。今回は、これまでのiPhoneとiPhone 7の中身を比較しつつ、どうして“大変身”が成されたのかを考察していこう。 SanDiskが語る、ストレージ・クラス・メモリの信頼性

SanDiskが語る、ストレージ・クラス・メモリの信頼性

SCMとはストレージ・クラス・メモリの略称で、性能的に外部記憶装置(ストレージ)と主記憶(メインメモリ)の間に位置するメモリである。前回は、SanDiskの講演から、SCMの性能とコストに関する比較をメモリセルレベルまで検討した。今回、信頼性について比較した部分をご紹介する。 TSMC、Apple「A10/A11」をほぼ独占的に製造か

TSMC、Apple「A10/A11」をほぼ独占的に製造か

TSMCは、Appleの「iPhone」向けプロセッサ「A10」および「A11」(仮称)の製造を、ほぼ独占的に製造することになるとみられている。もう1つのサプライヤーであるSamsung Electronics(サムスン電子)に対する優位性をもたらしたのは、独自のパッケージング技術「InFO」だという。 FinFETサイズの物理的な限界は?

FinFETサイズの物理的な限界は?

ベルギーで開催された「IMEC Technology Forum(ITF) 2016」では、2.5D(2.5次元)のチップ積層技術や、FinFETのサイズの物理的な限界についても触れられた。