マイコンからHPCまで――RISC-Vが目指す“懐の深さ”:RISC-V Day 2017 Tokyo(2/2 ページ)

2017年12月18日に、「RISC-V Day 2017 Tokyo(リスクファイブの1日)」が開催され、RISC-V会長のKrste Asanović氏らがRISC-Vについて講演を行った。本記事では、基調講演を一部抜粋して紹介する。

シンプルで、スケーラビリティが高い構造

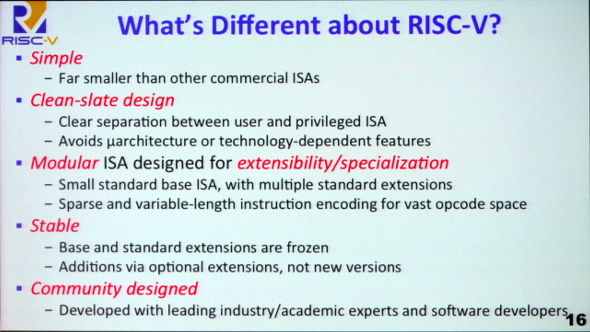

Asanović氏はRISC-Vの特長として、ライセンスがオープンであることだけでなく、シンプルであること、スケーラビリティが高いことを紹介した。

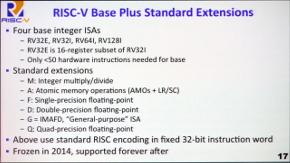

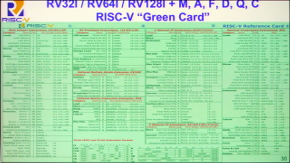

RISC-Vは、小規模でシンプルな4つの整数ISA(RV32E, RV32I, RV64I, RV128I)を用意し、機能追加は標準拡張ISA(整数の乗除算を提供するM, アトミックなメモリアクセスを提供するA, 単精度浮動小数点演算を提供するF, 倍精度浮動小数点演算を提供するD, 4倍精度浮動小数点演算を提供するQ、組み込み用途向けに命令長を16ビットに圧縮したCなど)で実現するモジュラー構造を取る。この整数ISAと標準拡張ISAは、2014年に仕様が凍結し永久にサポートされるという。

これにより、RISC-Vを用いたチップの設計者は、必要な機能を提供するISAのみを実装できるというメリットがある。また、可変長命令をサポートした空のオペコードも用意されているため、第三者による拡張命令セットの実装も可能だ。

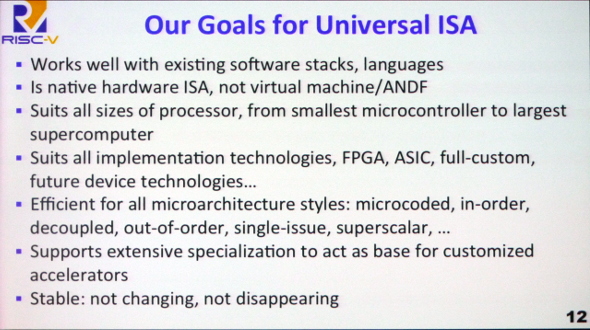

このような特長を持ちつつ、現在用いられているプログラミング言語への幅広い対応や、マイコンからHPC(High Performance Computing)まで単一のISAでサポートできること、FPGAやASIC、フルカスタムといった実装方法に全て適合することを目標として、RISC-Vの開発を進めてきたという。

Asanović氏は講演の終盤で、インドにおいて国家標準ISAとしてRISC-Vへの投資が進んでいることや、NVIDIAが将来のGPUにRISC-Vを採用するとアナウンスしたことにも触れており、エコシステムが広がりつつあることを強調する。また、コンピュータ技術に関する教本として名高いJohn L.Hennessy氏とDavid A.Patterson氏の共著「Computer Architecture」第6版にも、RISC-Vが命令セットの解説に採用されたことを紹介した。

RISC-V Day 2017 Tokyoでは、RISC-Vを採用し4096コアを搭載したHPC用プロセッサを開発するEsperanto社で技術メンバーを務める笠原栄二氏も講演をしており、こちらも別途紹介する予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

関心高まるRISC-V、Armやx86の代替となり得るか

関心高まるRISC-V、Armやx86の代替となり得るか

2017年11月28〜30日にかけて、米国シリコンバレーで「7th RISC-V Workshop」が開催された。オープンな命令セットアーキテクチャ「RISC-V」は、Arm系やx86系の命令セットの代替となり得る技術として確実に台頭してきている。 RISC-Vベースチップ手掛ける新興企業が資金調達

RISC-Vベースチップ手掛ける新興企業が資金調達

RISC-VアーキテクチャをベースのCPUコアやカスタムSoCなどを手掛ける米国の新興企業SiFiveが合計1350万米ドルの資金を調達した。 Microsemi、FPGA向けのRISC-V IPコアを提供へ

Microsemi、FPGA向けのRISC-V IPコアを提供へ

Microsemi(マイクロセミ)が、同社のFPGA「IGLOO2」「RTG4」やSoC FPGA「SmartFusion」などに向けた、RISC-VのソフトウェアIPコアを発表した。 ムーアの法則の終息でIDMの時代に“逆戻り”か?

ムーアの法則の終息でIDMの時代に“逆戻り”か?

米国サンフランシスコで開催されたコンピュータ関連のイベントで、半導体業界の専門家たちがパネルディスカッションを行い、「ムーアの法則」を中心に業界の今後について議論した。専門家の1人は、Appleの動きや、近年の大規模なM&Aの動きから、半導体業界はIDM(垂直統合型)に近い形に“逆戻り”するのだろうか、との疑問を投げかけた。 MIPSコンピュータをめぐる栄枯盛衰

MIPSコンピュータをめぐる栄枯盛衰

RISCプロセッサの命令セットアーキテクチャである「MIPS」。そのMIPSを採用したワークステーションの開発には、日本企業も深く関わった、栄枯盛衰の歴史がある。 Imaginationが身売りへ、Appleの取引停止宣告余波

Imaginationが身売りへ、Appleの取引停止宣告余波

AppleからGPUコアの技術利用停止の通達を受けたImagination Technologiesが、全社売却を決定した。Appleの通達を受けたとImaginationが発表してから、わずか2カ月後のことだ。