技術講演の最終日午前(その2)、ついに1Tビットに到達した3D NANDフラッシュ:福田昭のデバイス通信(133) 2月開催予定のISSCC 2018をプレビュー(9)(2/2 ページ)

「ISSCC 2018」最終日午前の講演から、セッション19と20を紹介する。シリコン面積が0.00021平方mmと極めて小さな温度センサーや、3D(3次元) NANDフラッシュメモリの大容量化および高密度化についての論文が発表される。

積層数を96層と高層化した3D NANDフラッシュ技術

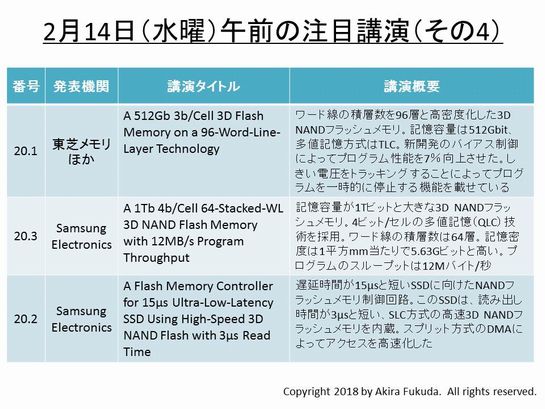

セッション20の「フラッシュメモリ」では、3D(3次元) NANDフラッシュメモリの大容量化技術と高密度化技術が続出する。

東芝メモリと東芝メモリシステムズ、Western Digitalの共同研究グループは、ワード線の積層数を96層と高密度化した3D NANDフラッシュメモリを発表する(講演番号20.1)。記憶容量は512Gビット、多値記憶方式はTLC(3ビット/セル)である。新開発のバイアス制御によってプログラム性能を7%向上させた。しきい電圧をトラッキングすることによってプログラムを一時的に停止する機能を載せている。

Samsung Electronicsは、記憶容量が1Tビットと大きな3D NANDフラッシュメモリを開発した(講演番号20.3)。4ビット/セルの高密度な多値記憶(QLC)技術を採用することによって記憶容量を拡大している。ワード線の積層数は64層。記憶密度は1mm2当たりで5.63Gビットと高い。プログラムのスループットは12Mバイト/秒。

Samsung Electronicsはまた、遅延時間が15マイクロ秒と短いSSD(Solid State Drive)に向けたNANDフラッシュメモリ制御回路を報告する(講演番号20.2)。読み出し時間が3マイクロ秒と短い3D NANDフラッシュメモリを使う。これは同社が「Z-NAND」と呼ぶ3D NANDフラッシュ技術(SLC記憶の高速3D NANDフラッシュ技術)を採用したメモリだとみられる。制御回路は、スプリット方式のダイレクトメモリアクセス(DMA)に対応することでメモリアクセスを高速化した。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

東芝がQLCの3D NANDを試作、96層プロセスの開発も

東芝がQLCの3D NANDを試作、96層プロセスの開発も

東芝メモリは、同社の3D NAND型フラッシュメモリ「BiCS FLASH」について、4ビット/セル(QLC)技術を用いた試作品と、96層積層プロセスを用いた試作品を開発し、基本性能を確認したと発表した。 東芝、TSVを採用した1Tバイトの3D NANDを試作

東芝、TSVを採用した1Tバイトの3D NANDを試作

東芝メモリが、複数の半導体チップを1つのパッケージ内で積層する「TSV(Through Silicon Via)」を活用し、総容量1Tバイトの3次元フラッシュメモリのプロトタイプを開発した。 東芝、日米韓連合にメモリ事業を売却

東芝、日米韓連合にメモリ事業を売却

東芝は、東芝メモリ(TMC)の売却契約を、日米韓企業連合と締結したと発表した。 まとめ:新世代のメモリを創造する二酸化ハフニウム/ジルコニウム

まとめ:新世代のメモリを創造する二酸化ハフニウム/ジルコニウム

今回は、強誘電体メモリに関する2つのシリーズ「強誘電体メモリの再発見」と「反強誘電体が起爆するDRAM革命」の要点をまとめる。2011年に二酸化ハフニウム強誘電体が公表されてからの研究成果を振り返るとともに、これからの課題についても触れておきたい。 究極の高密度不揮発性メモリを狙う強誘電体トランジスタ

究極の高密度不揮発性メモリを狙う強誘電体トランジスタ

今回は、1個のトランジスタだけでメモリセルを構成できる「FeFET(Ferroelectric FET)」または「強誘電体トランジスタ」について解説する。FeFETは、構造はシンプルだが、トランジスタの設計はかなり複雑になる。 MRAMの記憶素子「磁気トンネル接合」

MRAMの記憶素子「磁気トンネル接合」

今回は、磁気トンネル接合素子に焦点を当てる。磁気トンネル接合素子においてどのように2値のデータを保持できるのか、その仕組みを解説したい。