半導体メモリのチップとパッケージとシリコンダイ(前編):福田昭のデバイス通信(139)(2/2 ページ)

「チップ」「デバイス」という単語から想像するイメージは、業界やコミュニティーによってずれがある。では、どのようなずれがあり、なぜ、ずれが生じたのだろうか。

半導体の「チップ」から想起するイメージの違い

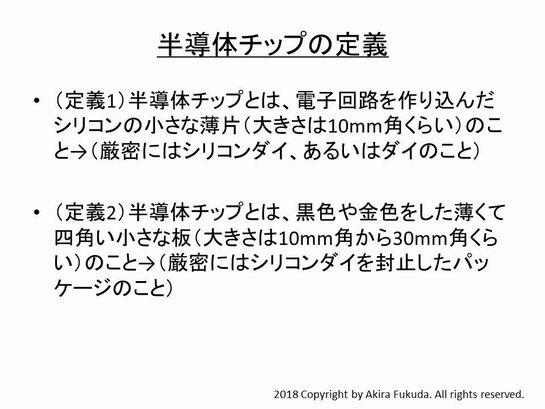

半導体デバイスはしばしば、「チップ」あるいは「半導体チップ」と呼称される。「半導体チップ」という単語から想像するイメージは、人によってズレがある。シリコンダイを想起する人もいれば、パッケージに入った製品を想起する人もいる。文書に「半導体チップ」と記述してあったときに、それだけでどちらなのかを判断することは、簡単ではない。

筆者が半導体産業をウォッチしてきた経験からは、1980年代に「チップ」と言えば、それはシリコンダイを意味することが多かった。ところが2000年代には、「チップ」の意味は曖昧になり、パッケージに入った製品を意味することが多くなっていたように思う。

1990年代にPCの普及によって一般消費者が半導体デバイス、特にマイクロプロセッサとDRAMに馴染んだことが、意味合いの変化に関連しているようだ。PCを趣味とするコミュニティーでは、半導体デバイスを「チップ」と呼ぶようになっていたからだ。彼らは半導体デバイスを「パッケージ」とは呼ばない。もちろん「シリコンダイ」とも呼ばない。PCを趣味とするユーザーの多くは、半導体デバイスの内部構造には関心を持たない。その関心の無さがシリコンダイとパッケージの区別を曖昧にし、「チップ」という用語の変質を招いたともいえる。

PCの世界で「半導体デバイス」という用語が使われなかった理由

半導体の世界では、「半導体デバイス」という呼び方が珍しくない。しかしPCの世界では「半導体デバイス」という用語は普及しなかった。PCの世界では「デバイス」は、サブシステムを意味したからだ。プリンタや磁気ディスク、スキャナーなどが「デバイス」なのである。半導体は「デバイス」ではない。

半導体のコミュニティーを取材することから社会人を始めた筆者にとって「チップ」がシリコンダイではなく、半導体デバイスそのものを指す、という事実にはかなりの違和感を覚えた。だが、PCを趣味とする人の数は、半導体のコミュニティーに属する人の数よりもはるかに多い。多勢に無勢であり、半導体のコミュニティーに勝ち目はなかった。

そして「チップ」はシリコンダイではない、別の何かに変貌した。例えばDIMMボードに並んで載せられている黒色の四角い板状のもの。それがDRAMの「チップ」なのだ。FCBGAパッケージに封止されたDRAM、TSOPに封止されたDRAMなどという細かいことには関心がなく、「チップ」と呼ぶ人が多数を占める。そういう時代になったということだろう。

(後編に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

DRAMについて知っておくべき、4つのこと

DRAMについて知っておくべき、4つのこと

今回は、DRAMで知っておくべき4つの事実を紹介する。「DRAMの事業規模は巨大であること」「DRAMの性能は常に不足していること」「DRAM開発は傾斜が急になり続ける坂道を登っているようなものであること」「3次元技術はDRAM開発にとって援軍ではあるが救世主ではないこと」の4つだ。 IEDM 2017の記者室にVLSIシンポジウムの実行委員会が乱入

IEDM 2017の記者室にVLSIシンポジウムの実行委員会が乱入

2017年12月のこと。米国サンフランシスコで開催される「IEDM 2017」で、米国ハワイで2018年6月に開催する「VLSIシンポジウム」の非公式ブリーフィングを行うという、何とも不思議な案内状が届いた。一体、どういうことだったのか。 2017年半導体メーカーランキング(速報版)

2017年半導体メーカーランキング(速報版)

米調査会社のGartner(ガートナー)は2018年1月4日、2017年の半導体メーカー別売上高ランキング(上位10社)を発表した。 東芝、メモリなき営業益はトントンだが過去最高益更新へ

東芝、メモリなき営業益はトントンだが過去最高益更新へ

東芝が2018年2月14日に発表した2018年3月期(2017年度)第1〜3四半期(4〜12月)業績と、2017年度通期業績予想の修正を発表した。 TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

TSMCの高性能・高密度パッケージング技術「CoWoS」(前編)

今回から前後編に分けて「CoWoS(Chip on Wafer on Substrate)」を解説する。CoWoSの最大の特長はシリコンインターポーザを導入したことだが、では、なぜシリコンインターポーザが優れているのだろうか。シリコンインターポーザに至るまでの課題と併せて説明する。 2.5D(2.5次元)の新世代パッケージング技術

2.5D(2.5次元)の新世代パッケージング技術

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。