連載

メモリホールにおけるエッチングと成膜の難度を軽減する2つの手法:福田昭のストレージ通信(128) 3D NANDのスケーリング(14)(2/2 ページ)

3D NANDフラッシュメモリの高密度化と大容量化を実現する手法について、技術的な難度を低減する2つの方法を解説する。

ペア薄膜の厚みを減らす

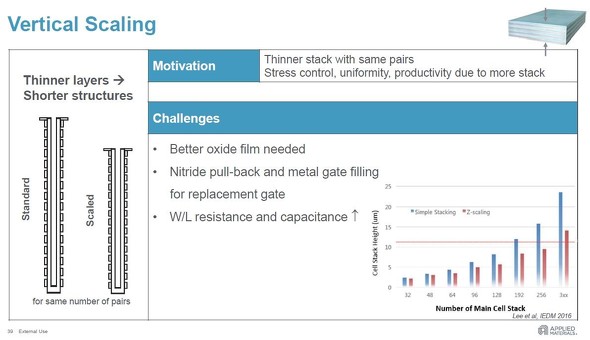

次に紹介するのは、ペア薄膜の厚みを減らす手法である。「バーティカル・スケーリング(Vertical Scaling)」と呼ばれる。

ペア薄膜を構成する制御ゲート(ワード線)層と絶縁層の厚みを減らすと、同じペア数でも全体の高さが減少する。するとエッチングのアスペクト比が下がる。この結果、メモリホールのエッチングと成膜の技術的な難度が緩和される。

もちろん、課題はある。厚みを減らすと制御ゲート(ワード線)の電気抵抗と寄生容量が増大する。また、隣接するセル間の電気的な干渉が増加する。そして絶縁膜を薄くしても品質を維持する必要がある。こういった課題に対処しなければならない。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

垂直方向に並んだセルトランジスタを一気に作る

垂直方向に並んだセルトランジスタを一気に作る

3D NANDフラッシュ製造におけるキープロセスの1つ、「メモリセルの形成(Cell Formation)」技術について解説する。 高アスペクト比の細長い孔をハードマスクによって形成(続き)

高アスペクト比の細長い孔をハードマスクによって形成(続き)

前回に続き、3D NANDフラッシュ製造におけるキープロセスの1つ、「高アスペクト比(HAR:High Aspect Ratio)のパターン形成」を取り上げる。今回は、同技術の異方性エッチングについて解説する。 Intelは「データの移動・保存・処理」で貢献

Intelは「データの移動・保存・処理」で貢献

Intelの日本法人であるインテルは2018年12月17日、都内で開催した記者説明会で2018年の活動の振り返りと今後の展望について説明した。 大幅に消費電力を低減したFRAMを発表

大幅に消費電力を低減したFRAMを発表

Cypress Semiconductor(サイプレス セミコンダクタ)は2018年11月14日に開幕した展示会「ET&IoT Technology 2018」(会場:パシフィコ横浜/会期:2018年11月16日まで)で、超低消費電力を特長にしたFRAM(強誘電体メモリ)の新製品「Excelon LP F-RAM」を発表した。 DRAMの価格下落が加速

DRAMの価格下落が加速

メモリチップ価格の追跡を手掛ける市場調査会社TrendForceによると、DRAM価格は2018年第4四半期(10〜12月)に同年前期比で約5%下落する見込みだという。 2018年の半導体売上高、過去最高となる見込み

2018年の半導体売上高、過去最高となる見込み

SEMIによると、2018年における半導体売上高は4700億米ドルに達し、2017年に続き過去最高を更新する見込みだという。