半導体ヘテロ構造を用いた高効率冷却素子を開発:冷却能力はペルチェ素子の約10倍

東京大学らの研究グループは、半導体へテロ構造を用いて、効率が高い冷却素子を開発した。従来のペルチェ素子に比べ約10倍の冷却能力を持つという。

デバイス活性層を局所的かつ高効率に冷却する

東京大学生産技術研究所光物質ナノ科学研究センターの平川一彦教授とLIMMS/CNRS-IIS(UMI2820)国際連携研究センターのベスコン・マーク国際研究員を中心とする研究グループは2019年10月、半導体へテロ構造を用いて、効率が高い冷却素子を開発したと発表した。従来のペルチェ素子に比べ約10倍の冷却能力を持つという。

固体冷却素子として、熱電効果を用いたペルチェ素子が実用化されている。しかし、発熱する高性能LSIを効率よく冷却するには十分ではなかった。データセンターやスーパーコンピュータは、システム全体を冷房して過熱による性能低下を防いでいるが、そのために膨大なエネルギーを消費しているという。

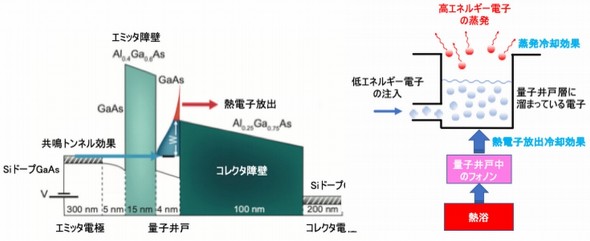

そこで研究グループは、より高い冷却効率を実現するため、熱電子放出冷却(thermionic cooling)技術に注目した。GaAs/AlxGa1-xAsへテロ構造を適切に設計し、共鳴トンネル効果と熱電子放出を制御する技術である。

具体的な動作原理はこうだ。厚み15nmのエミッタ障壁層(Al0.4Ga0.6As層)から、共鳴トンネル効果によって電子が量子井戸層内の量子化準位に注入される。量子井戸層内で熱分布をした電子のうち、厚み100nmのコレクタ障壁層(Al0.25Ga0.75As層)のエネルギー障壁を超えた熱電子だけが、コレクタ電極に脱出する。

こうした熱電子放出によって、量子井戸層内の電子はエネルギーを奪われて温度が下がる(蒸発冷却)。この時に、電子系と量子井戸内の結晶格子系が相互作用し、格子系も冷却される(熱電子放出冷却)という。

研究グループは、フォトルミネセンス分光法を用い、量子井戸内における電子系の温度を評価する実験を行った。作製した非対称二重障壁半導体ヘテロ構造にレーザー光を照射し、電圧の関数として素子からのフォトルミネセンスを測定した。また、フォトルミネセンスピークの高エネルギー側のスペクトル形状から、電子系温度を評価した。

この結果、バイアス電圧の印加にかかわらず、電極内の電子温度はほぼ室温で一定となった。ところが量子井戸からの発光に対しては、バイアス電圧を印加していくとスペクトルの裾野の傾きが急になり、電子温度が300Kから250Kまで、約50Kも低下することを確認した。この値は熱非平衡の電子・格子系を扱う詳細な理論計算とも一致したという。

研究グループは今回の成果について、トランジスタや半導体レーザーなどのデバイス活性層を、局所的に効率よく冷却する新しい素子技術であり、エネルギー削減やデバイスの性能改善に大きく貢献するとみている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

東京大学、新たな電子伝導現象を発見

東京大学、新たな電子伝導現象を発見

東京大学は、非磁性半導体と強磁性半導体からなる二層ヘテロ接合を作製し、新たな電子伝導現象を発見した。磁気抵抗効果は従来に比べ約800倍の大きさになることを確認した。 東大、高分子半導体でイオン交換現象を発見

東大、高分子半導体でイオン交換現象を発見

東京大学大学院新領域創成科学研究科の研究チームは、半導体プラスチック(高分子半導体)でもイオン交換が可能なことを発見した。 東京大学、従来比2桁小さい電流密度で磁化反転

東京大学、従来比2桁小さい電流密度で磁化反転

東京大学は、強磁性半導体単層極薄膜に小さい電流を流すだけで、磁化の向きが反転する現象を発見した。 東大ら、ナノチューブで巨大な光起電力効果発見

東大ら、ナノチューブで巨大な光起電力効果発見

東京大学らの共同研究グループは、二硫化タングステンナノチューブにおいて、バルク光起電力効果(BPVE)が大幅に増幅されることを発見した。 東大ら、低欠陥InGaAs/GaAsナノ円盤構造を作製

東大ら、低欠陥InGaAs/GaAsナノ円盤構造を作製

東京大学大規模集積システム設計教育研究センター(VDEC)の肥後昭男特任講師らによる研究グループは、バイオテンプレートと中性粒子ビームエッチング技術を組み合わせて、欠陥が少ないInGaAs/GaAs(インジウムガリウムヒ素/ガリウムヒ素)ナノ円盤構造(量子ドット)を作製することに成功した。 東大生研、大容量&低消費電力のFeFETを開発

東大生研、大容量&低消費電力のFeFETを開発

東京大学生産技術研究所は2019年6月10日、大容量で低消費電力な8nmの極薄IGZOチャネルを有するトランジスタ型強誘導体メモリ(FeFET)を開発した、と発表した。同所は、「IoTデバイスのエネルギー効率が飛躍的に向上し、より高度で充実したネットワーク、サービスの展開が期待される」としている。