パッケージの多端子化と小型化、薄型化、低コスト化が進む:福田昭のデバイス通信(213) 2019年度版実装技術ロードマップ(24)(2/2 ページ)

今回は第3章「電子デバイスパッケージ」から、各種パッケージの技術動向を紹介する。半導体パッケージの歴史は、多端子化と小型化、薄型化、低コスト化の歴史でもある。

WL-CSPとFO-WLPが適用範囲を拡大

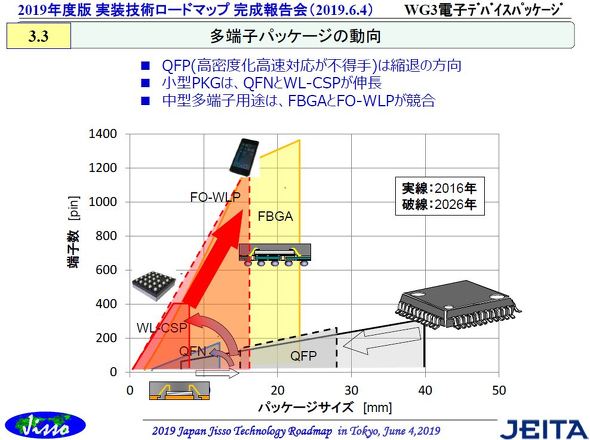

半導体パッケージの歴史とは、多端子化と小型化、薄型化、低コスト化の歴史だとも言える。多端子化では、BGAを高密度化した「FBGA(Fine-pitch BGA)」が1000端子(ピン)を超える入出力端子を表面実装型で実現した。それまでの主流であったQFPの端子数は、最大で300ピン前後だった。さらにQFPでは長いリードによる寄生素子とインピーダンス不整合が、高速化を妨げていた。FBGAはパッケージ基板が配線基板なのでインピーダンスの制御が容易であり、配線長が短い。高速動作に適している。

小型化では、ウエハーレベルでシリコンダイに近い寸法のパッケージを製造する「WL-CSP(Wafer Level-Chip Scale Package)」が開発され、100ピン前後では主流となっている。WL-CSPはウエハーレベルで一括製造することから、パッケージのコストを大きく下げることにも成功した。

WL-CSPの弱点は端子ピッチの狭さにある。これはプリント配線基板の製造を難しくする。さらに、シリコンダイの寸法に対して入出力端子数が多くなると、全ての端子を収容できなくなるという問題が生じる。

そこで開発されたのが、シリコンダイの入出力パッドから端子を外側に引き出す「FO-WLP(Fan Out-Wafer Level Package)」である。今後はFO-WLPが、400ピンを超えるような多端子の領域で普及していく。

また最近の重要なトレンドに、複数のシリコンダイを1個のパッケージにまとめる「SiP(System in Package)」がある。SiPは、1枚のシリコンダイに複数の機能を内蔵するSoC(System on a Chip)と比較されることが多い。SiPは機能別、あるいは製造技術別に異なるシリコンダイを組み合わせるので、SoCに比べると開発期間が大幅に短く、製造コストでも有利になることが少なくない。一方で一定数量を超える生産が見込め、製造プロセスがあまり複雑にならない場合は、SoCが製造コストで有利になる。また小型化と薄型化では、当然ながらSoCが優位に立つ。

SiPには数多くの実現技術が存在する。PoP(Package on Package)、FO-WLP、FBGA、3次元(3D)積層、2.X次元(2.XD)積層などである。

(次回に続く)

⇒「福田昭」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

エレ実装関連の世界市場、2025年に10兆円市場へ

エレ実装関連の世界市場、2025年に10兆円市場へ

エレクトロニクス実装関連の世界市場は2025年に10兆1451億円へ――。富士キメラ総研が半導体パッケージ関連材料やプリント配線板および、関連材料などの市場予測をまとめた。 IoT社会に向けて多様化する電子デバイスパッケージ

IoT社会に向けて多様化する電子デバイスパッケージ

今回から、第3章「電子デバイスパッケージ」の概要を説明していく。「2019年度版 実装技術ロードマップ」で約70ページが割かれている重要な章だ。序章では、年間で1兆個のセンサーが生産される「トリリオンセンサー」について言及している。【訂正あり】 第5世代(5G)移動通信システムへの移行と課題

第5世代(5G)移動通信システムへの移行と課題

前回に続き、「第5世代(5G)移動通信システム」の内容を紹介するシリーズ。今回は、4G(第4世代)から5Gへの移行シナリオについて説明する。 2020年3月期上期 国内半導体商社 業績まとめ

2020年3月期上期 国内半導体商社 業績まとめ

半導体や電子部品、電子機器などを扱う主要な国内半導体/エレクトロニクス商社(集計対象:22社)の2020年3月期上期業績は、長引く米中貿易摩擦や中国経済の減速などの影響で、14社が前年同期の売上高を下回る減収になった。【訂正あり】 2.5D(2.5次元)の新世代パッケージング技術

2.5D(2.5次元)の新世代パッケージング技術

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。 Intelが3つの次世代パッケージング技術を明らかに

Intelが3つの次世代パッケージング技術を明らかに

Intelは、米国カリフォルニア州サンフランシスコで2019年7月9〜11日の日程で開催されている「SEMICON West 2019」に合わせて行われたイベントにおいて、3種類のパッケージング技術に関する同社のロードマップを初めて明らかにした。