連載

異種デバイスの融合を実現する3次元集積化技術:福田昭のデバイス通信(296) Intelが語るオンチップの多層配線技術(17)(2/2 ページ)

今回は、異種デバイスの融合を実現する3次元(3D)集積化技術の概要を説明する。

5μm以下のピッチを目指せるハイブリッド接合

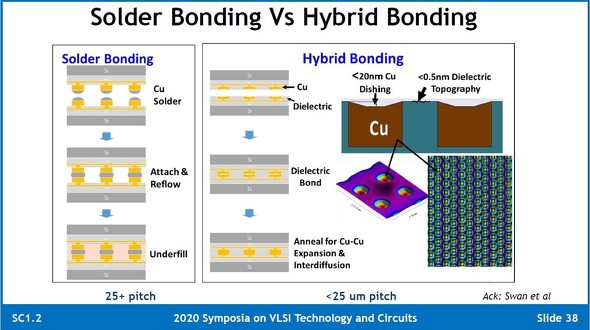

はんだ接合とハイブリッド接合の工程を見てみよう。はんだ接合では、表面に飛び出したCu電極の上に、はんだ(Solder)のバンプを形成する。それからはんだバンプ同士を対向接触させ、はんだの加熱溶融と再固化によって電気的な接続と機械的な接続の両方を実現する。最後に、残った空間に樹脂(アンダーフィル)を充填して完成である。

ハイブリッド接合では、はんだバンプは使わない。表面はCu電極と絶縁膜で構成する。Cu電極の表面は食器の皿のようにくぼんでいる。くぼみの深さは20nm以内である。絶縁膜表面はほんのわずかだけ、削る。削る深さは0.5nm以内と非常に浅い。

このような前処理を施したシリコンのCu電極側表面同士を対向接触させる。すると絶縁膜同士が接続される。対向するCu電極間にはわずかな隙間が残る。次にシリコン同士を圧着したまま加熱処理すると、対向するCu電極が膨張して接触し、相互拡散によって接合を形成する。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

露光技術の微細化限界を突破する自己組織化技術

露光技術の微細化限界を突破する自己組織化技術

今回から、ArF液浸技術やEUV(極端紫外線)技術などの露光技術の微細化限界を超える、あるいはこれらの露光技術を延命させる次世代のリソグラフィ技術「自己組織化リソグラフィ」をご紹介する。 多層配線の性能を向上させるエアギャップと2次元材料

多層配線の性能を向上させるエアギャップと2次元材料

今回は、多層配線の容量を下げる要素技術「エアギャップ」と、多層配線の抵抗を下げる要素技術「2次元(2D)材料」について解説する。 多層配線のアスペクト比(AR)を高める2つの要素技術

多層配線のアスペクト比(AR)を高める2つの要素技術

配線のアスペクト比(AR)を高める、2つの要素技術について解説する。 多層配線のアスペクト比(AR)と抵抗および容量の関係

多層配線のアスペクト比(AR)と抵抗および容量の関係

今回は、配線のアスペクト比(AR)と配線抵抗および配線容量の関係を概説する。 銅(Cu)配線の微細化と抵抗値の増大

銅(Cu)配線の微細化と抵抗値の増大

引き続き、オンチップの多層配線技術に関するIntelの講演内容を紹介する。今回は、銅配線の寸法と電気抵抗の関係を説明する。 ムーア則の維持に貢献する配線技術

ムーア則の維持に貢献する配線技術

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。