微細化の極限を目指すCMOSロジックの製造技術:福田昭のデバイス通信(298) imecが語る3nm以降のCMOS技術(1)(2/2 ページ)

「IEDM2020」から、imecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏の講演内容を紹介する。CMOSを3nm以下に微細化するための要素技術を解説する講演だ。

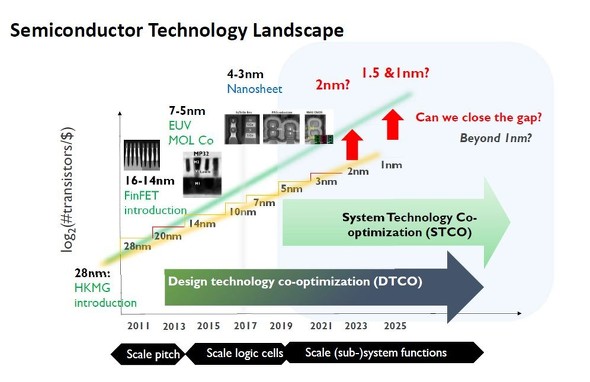

2025年までのCMOSロジック製造技術ロードマップ

ここからはチュートリアル講演の概要を説明していこう。Myung‐Hee Na氏は講演で始めに、CMOSロジック製造技術の微細化ロードマップをグラフで示した。時間軸(横軸)は2011年〜2025年の範囲である。縦軸には、製造コスト(米ドル)当たりのトランジスタ数を対数(2を底とする対数)で表示した。2019年の7nm技術までは、ほぼ一定の比率で、製造コスト当たりのトランジスタ数が増加してきたことが分かる。

CMOSロジックの微細化(技術ノード)と、トランジスタの製造コスト(ドル当たりのトランジスタ数、2を底とする対数目盛り)の推移。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)

このロードマップは、MOSトランジスタ技術の変遷をかなり具体的に説明している。28nm技術でプレーナー(平面)型MOSトランジスタはHKMG(高誘電体膜金属ゲート)技術を導入した。16/14nm技術でトランジスタが立体化し、FinFETとなった。以降はしばらく、FinFETの時代が続く。7nm技術〜5nm技術では、リソグラフィ技術を大きく変更した。従来のArFレーザー液浸リソグラフィ(とマルチパターニングの組み合わせ)に代わり、EUV(Extreme Ultraviolet:極端紫外線)リソグラフィ技術を導入した。またMOL(middle of the line)の配線材料にコバルト(Co)金属を採用し始めた。

4nm技術以降は、将来の時間領域に入る。4nm技術〜3nm技術のトランジスタはFinFETではなく、ナノシート構造のMOSトランジスタに変わると予想する。3nm以降のトランジスタ技術、すなわち2nm技術や1.5nm技術、1.0nm技術の候補はこのシリーズ連載で今後、説明していく。

ロードマップで注目すべきなのが、時間軸(横軸)の下にあるスケーリングに関する記述だ。28nm技術〜20nm技術までは、リソグラフィ技術によって配線とトランジスタのピッチを短くすることがスケーリング(トランジスタ密度の向上)を支える手段だった。しかし20nm以降は、ピッチの短縮があまり進まなくなる。そこでCMOSロジックの基本セル(スタンダードセル)の高さ(最下層配線の本数でカウントする)を下げることで、従来とほぼ同じペースの密度向上を維持してきた。だが既に、スタンダードセルの高さを下げる手法は難しくなりつつある。今後はサブシステムあるいは回路ブロックをスケーリングする手法に移行すると予測する。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 異種デバイスの融合を実現する3次元集積化技術

異種デバイスの融合を実現する3次元集積化技術

今回は、異種デバイスの融合を実現する3次元(3D)集積化技術の概要を説明する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。