Intelがプロセスの名称を変更、「nm」から脱却へ:パッケージング技術の最新情報も(2/2 ページ)

Intelは2021年7月26日(米国時間)、半導体プロセスとパッケージング技術の最新情報を説明するウェブキャスト「Intel Accelerated」を開催した。これを受けて、同社の日本法人インテルは7月28日に、Intel Acceleratedの内容を日本のメディア向けに説明するオンライン説明会を実施。インテル 執行役員常務 技術本部本部長である土岐 英秋氏が説明した。

GAAと新しい電源供給技術を導入

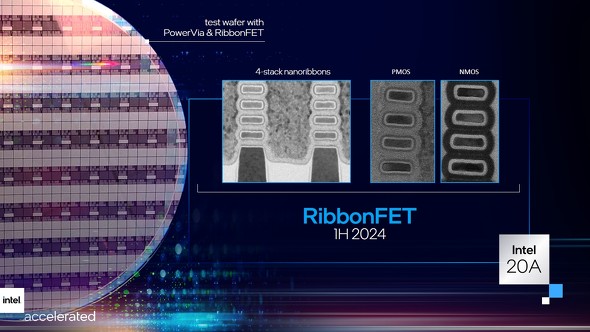

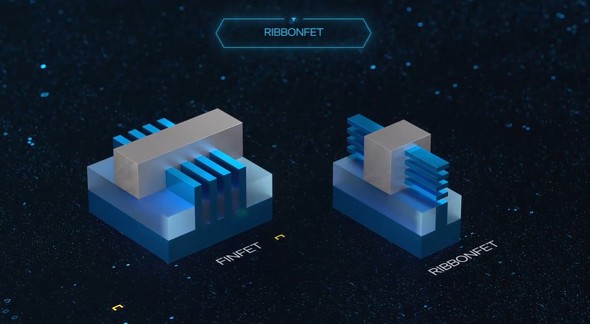

Intel 20Aから導入するRibbonFETは、チャネルをゲートで取り囲む、いわゆるGAA(Gate-All-Around)構造を持つFETである。GAAは、短チャネル効果耐性が強く、高い電流駆動能力を持つという利点がある。

Intelが「nanoribbon(ナノリボン)」と呼ぶチャネルを積層することで、同じ駆動電流を持つFinFETに比べ、実装面積が小さいRibbonFETを実現できる 出典:「Intel Accelerated」のウェブキャストのキャプチャー(クリックで拡大)

PowerViaは新しい電力供給技術だ。これまではICの中で混在していた電源配線と信号配線を分け、ウエハー裏面に電源配線を設ける。信号配線はこれまでのようにトランジスタの上部に積層する金属層に作り込む。このように、「電源配線と信号配線の“道筋”を分ける」(土岐氏)ことで、ICの設計がしやすくするだけでなく良好なシグナルインテグリティを実現できるとする。

「PowerVia」の概念。トランジスタの上部が信号配線(金色の線)で、電源配線(銅色の線)はウエハー裏面に作り込まれる 出典:「Intel Accelerated」のウェブキャストのキャプチャー(クリックで拡大)

次世代2.nD/3Dパッケージング技術

パッケージング技術の拡張も発表された。Intel独自の2.nD(2.n次元)のパッケージング技術である「EMIB(Embedded Multi-die Interconnect Bridge)」では、バンプのピッチが、現行世代の55μmから40μmまで狭くなる。つまり、より高密度になる。

次々世代のクライアント向けプロセッサである「Meteor Lake」には、3Dパッケージング技術「Foveros」が採用されるが、このバンプピッチは36μmで、5〜125WのTDP(Thermal Design Power)をサポート可能になる。なお、Intelが開発中のGPU「Ponte Vecchio(開発コードネーム)」には、EMIBとFoverosの両方が採用されている。

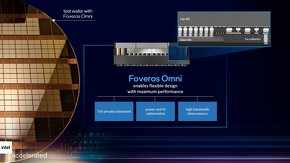

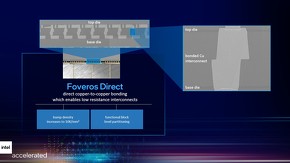

Foverosの次世代技術が「Foveros Omni」と「Foveros Direct」である。Foveros Omniは、上部のダイが、下部のダイを経由することなく基板に直接、TSV(シリコン貫通ビア)で接続される。これにより、より柔軟な設計や、電源および信号配線のさらなる最適化を図ることができる。Foveros Directでは、ダイを接続する際、はんだボールではなく銅線同士を直接接続させる。10μm未満のバンプピッチを実現でき、3D積層におけるインターコネクト密度を格段に上げられる。Foveros Omni、Foveros Directともに2023年の量産開始を予定している。

なお、Intel Acceleratedでは、IFSの顧客として、AWSがIntelのパッケージング技術を、QualcommがIntel 20Aプロセスを採用することも明らかになった。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

2021年上半期の半導体業界を振り返る

2021年上半期の半導体業界を振り返る

新型コロナウイルス感染症(COVID-19)は猛威をふるい続け、ワクチン接種という明るい兆しはあれど、感染の収束のメドは立たず厳しい状況は続いている。そうした中、COVID-19による勤務環境や生活環境の変化がけん引力となり、半導体市場は力強く回復している。今回は、半導体不足に加え、企業動向や技術動向も含め、2021年上半期を振り返ってみたい。 半導体/部品の供給不足で「値上げ」問題が浮き彫りに

半導体/部品の供給不足で「値上げ」問題が浮き彫りに

EE Times Japan、EDN Japan、MONOistのアイティメディア製造業向け3媒体は「半導体・電子部品の供給状況に関するアンケート」を実施した。調査期間は2021年2月17日〜3月16日で、有効回答数は201件。 Intelの高性能・高密度パッケージング技術「EMIB」の概要

Intelの高性能・高密度パッケージング技術「EMIB」の概要

今回は、Intelが開発した2.nD(2.n次元)のパッケージング技術「EMIB(Embedded Multi-die Interconnect Bridge)」を解説する。EMIBではシリコンインターポーザの代わりに「シリコンブリッジ」を使う。その利点とは何だろうか。 Intelが3つの次世代パッケージング技術を明らかに

Intelが3つの次世代パッケージング技術を明らかに

Intelは、米国カリフォルニア州サンフランシスコで2019年7月9〜11日の日程で開催されている「SEMICON West 2019」に合わせて行われたイベントにおいて、3種類のパッケージング技術に関する同社のロードマップを初めて明らかにした。 Gelsinger氏の“帰還”、Intelにとっては好機か

Gelsinger氏の“帰還”、Intelにとっては好機か

CEO(最高経営責任者)の継承は、非常に重要である。最近の報道によると、IntelのCEOであるBob Swan氏が近々退任し、その後任としてPat Gelsinger氏が就任するという。一方Qualcommは、現プレジデントであるCristiano Amon氏にCEOの後任を託すとしている。 Intelが車載半導体生産で協議中、ロイターが報道

Intelが車載半導体生産で協議中、ロイターが報道

Reuters(ロイター通信)は2021年4月12日(米国時間)、Intelが、自動車向け半導体を生産するための協議に入っていると報じた。IntelのCEOであるPat Gelsinger氏が、Reutersに明かしたという。