10nm以下の極短チャンネルを目指す2次元(2D)材料のトランジスタ:福田昭のデバイス通信(317) imecが語る3nm以降のCMOS技術(20)(2/2 ページ)

今回は、2次元材料の特長と、集積回路の実現に向けた課題について紹介する。

層状の遷移金属ダイカルコゲナイドをチャンネルに使う

MOSFETでは、チャンネルを短くするとしきい電圧が低下するという「短チャンネル効果」が微細化を阻害する。対策としてはチャンネルを薄くすることが考えられる。ただしシリコン(Si)のチャンネルはあまり薄くするとキャリアの移動度が下がる恐れがある。

2次元材料は単原子層と薄い。このため原理的には短チャンネル効果が起きにくい。またキャリアが2次元方向にしか流れないので、移動度がシリコン(ある程度の厚みがある状態)と同等以上であることが期待できる。

2次元材料でも当然ながら、半導体がトランジスタのチャンネルに使われる。前回で述べたように、遷移金属(Transition Metal)とカルコゲナイド(Chalcogenide)の化合物「遷移金属ダイカルコゲナイド(TMD)」が2次元の半導体材料であり、チャンネル材料の有力な候補でもある。具体的には「二流化タングステン(WS2)」や「二流化モリブデン(MoS2)」などが研究対象となっており、実際にトランジスタを試作して特性が評価されている。

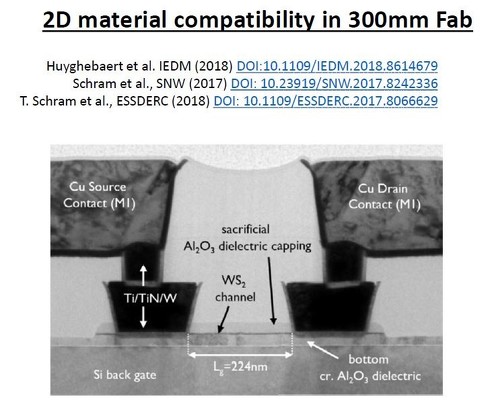

試作した2次元(2D)材料トランジスタの断面を電子顕微鏡で観察した画像。チャンネル(中央下)の材料は二流化タングステン(WS2)。チャンネルの下がアルミナのゲート絶縁膜、その下がシリコンのバックゲート。チャンネルのゲート長は224nm。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

集積回路の実現に向けた課題は山積

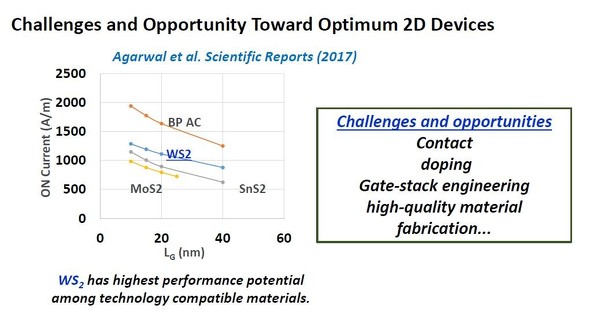

試作されている2Dトランジスタ(FET)の構造は、かなり基本的なものだ。バックゲート構造やデュアルゲート構造などが使われる。これらの構造は特性評価には適しているものの、集積回路には適していない。低抵抗コンタクトの形成、不純物拡散(ドーピング)の制御、ゲートスタックの制御、高品質な薄膜の成長技術など、量産に適した集積回路の具現化と商用化に向けた課題は山積している。

さまざまな2次元(2D)材料をチャンネルとするFETのオン電流とゲート長の比較(左)と、2D FETの課題(右)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

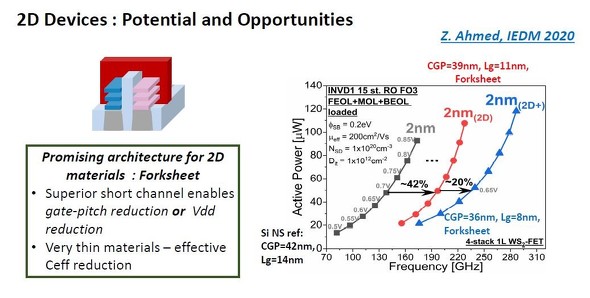

そのような中、imecは講演でフォークシート構造のナノシートチャンネルに二流化タングステン(WS2)を組み込み、シミュレーションによって特性を評価してみせた。シリコンのナノシート構造FETに比べ、二流化タングステン(WS2)のFETは同じ消費電力でも高い周波数で動作した。将来に期待を持たせる結果だ。

2次元材料の二流化タングステン(WS2)をフォークシート構造のナノシートに適用したFETの構造と高周波特性をシリコンのナノシート構造FETと比較した。左はフォークシート構造の概念図。右は動作周波数(横軸)と動作時消費電力(縦軸)の関係。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス エレクトロニクスは2021年7月29日、2021年12月期第2四半期(4〜6月)業績(Non-GAAPベース)を発表した。第2四半期3カ月間の売上高は2179億円で前年同期比30.7%増、営業利益は614億円で同2.03倍と大幅な増収増益になった。売上総利益率は52.0%、営業利益率は28.2%だった。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。