CMOS多層配線の高密度化を支えるビア電極の微細化:福田昭のデバイス通信(321) imecが語る3nm以降のCMOS技術(24)

今回は、多層配線技術の中核を成すビア電極技術について解説する。

多層配線の微細化にはビア電極の低抵抗化が不可欠

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。第21回から「次世代の多層配線(BEOL)技術」の講演パートを紹介している(クリックで拡大)

本シリーズの第21回から、5番目のパートである「次世代の多層配線(BEOL)技術」の講演内容を紹介している。3nm以降の技術世代(技術ノード)を担う多層配線技術を主題とする。前回では、銅(Cu)配線の次を担う有力候補とimecが見なす、「ルテニウム(Ru)配線技術」の微細化ロードマップと、配線層および絶縁層の要素技術を解説した。今回は、多層配線技術の中核を成すビア電極技術について述べる。

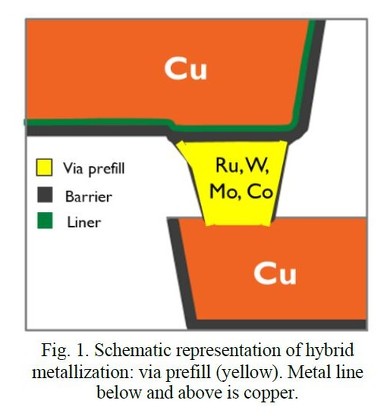

ビア電極は、上下の配線層を接続する円柱状の電極を指す。配線層間の絶縁膜に形成した細長い孔と、孔に埋め込んだ金属によって構成する。ビア電極の直径は通常、配線層の幅よりも短い。多層配線の配線幅を短くすると、ビア電極の抵抗は増加し、エレクトロマイグレーション耐性が低下する。銅(Cu)の多層配線を微細化すると、Cuビア電極の抵抗が著しく増加するとともに、エレクトロマイグレーション寿命が短くなる。そこでビア電極の金属だけを高融点金属に変更することが考えられている。このことは前々回でふれた。

配線層を銅(Cu)、ビア電極(黄色の部分)を高融点金属で形成する多層配線の断面構造図。出典:imec(IEDM 2020の発表論文「Inflection points in interconnect research and trends for 2nm and beyond in order to solve the RC bottleneck」(論文番号32.2)) (クリックで拡大)

多層配線のレイアウトとビア電極のレイアウト

最先端CMOSロジックの多層配線は、平行な直線配線群が上下の隣接層間で直交するレイアウトを採用していることが多い。例えば最下層(第1層あるいはM1)から奇数番号の層が水平(横)方向に伸び、偶数番号(第2層あるいはM2から始まる番号)の層が垂直(縦)方向に伸びる。一般的なビア電極は上下に隣接する配線層を接続するので、水平な配線と垂直な配線が交差する点に作製する。

しかし最近では、奇数番号(あるいは偶数番号)の上下に隣接する配線層を接続するビア電極が、必要とされるようになってきた。例えばM1とM3をビア電極で接続する。このようなビア電極には、下層側配線の電気抵抗を実効的に下げたり、エレクトロマイグレーション耐性を向上させたりする働きがある。

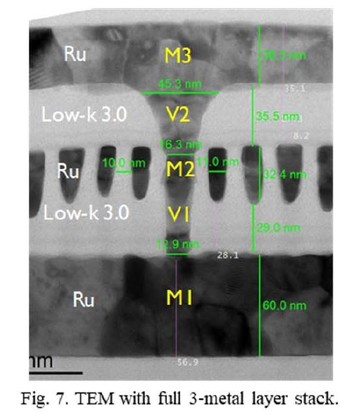

ルテニウム(Ru)で3層の多層配線を試作したときの断面を電子顕微鏡で観察した画像。断面の方向はM2(第2層)を横切るとともに、M1(第1層)とM3(第3層)に平行な方向である。配線ピッチはM1とM3が36nm、M2が21nm、ビア(V)の直径はV1(M1とM2を結ぶビア)が12.9nm、V2(M2とM3を結ぶビア)が16.3nm〜45.3nm。出典:imec(IEDM 2019の発表論文「Three-Layer BEOL Process Integration with Supervia and Self-Aligned-Block Options for the 3nm node」(論文番号19.3)) (クリックで拡大)

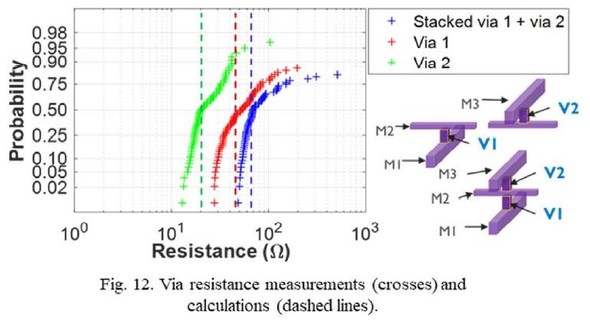

通常、3層配線の最下層と最上層は2つのビア電極と1つの配線層を重ねることで接続する。便宜上、M1とM2を結ぶビアを「V1」、「M2」と「M3」を結ぶビアを「V2」と記述しよう。平行な配線層であるM1とM3を結ぶには、2つのビアと1つの配線層を介する。V1、M2、V2である。M2はV1とV2の接続用なので細長い配線ではなく、柱状であることが多い。このような接続構造を「スタックビア(Stacked Via)」と呼ぶ。

ビア電極の電気抵抗値(累積確率)。ビア電極を試作して測定した出典:imec(IEDM 2019の発表論文「Three-Layer BEOL Process Integration with Supervia and Self-Aligned-Block Options for the 3nm node」(論文番号19.3)) (クリックで拡大)

imecが試作したRuの3層配線は、真ん中であるM2のピッチが最も狭い。このためV1の電気抵抗がやや高く、V2の電気抵抗がやや低い。そしてV1、M2、V2のスタックビアは電気抵抗が最も高い。

スタックビアの電気抵抗を下げる方法の1つは、M2を太くすることである。ただしM2をあまり太くすると周囲のM2を配置できず、レイアウトの自由度を阻害する。このほか、M2を介さずにM1とM3を直結する「スーパービア(SuperVia)」が考案されている。詳しくは次回に述べよう。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

微細化の極限を目指すCMOSロジックの製造技術

微細化の極限を目指すCMOSロジックの製造技術

「IEDM2020」から、imecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏の講演内容を紹介する。CMOSを3nm以下に微細化するための要素技術を解説する講演だ。 スマートフォンが搭載してきたNANDフラッシュの変遷

スマートフォンが搭載してきたNANDフラッシュの変遷

今回は、スマートフォンが搭載してきたNANDフラッシュメモリの変遷をたどる。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。