「InFO」構造を積層したミリ波帯域用高性能パッケージ:福田昭のデバイス通信(332) TSMCが開発してきた最先端パッケージング技術(5)(2/2 ページ)

今回から、さらに高い性能のコンピューティングに向けて「InFO」技術を改良した2種類のパッケージを解説する。

ミリ波帯域の挿入損失が25%〜30%減少

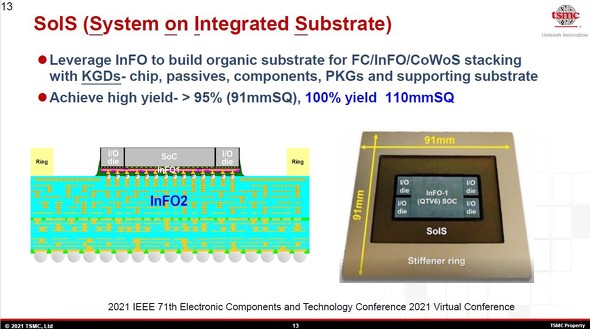

始めは2個の「InFO」構造を積層する「InFO_SoIS(System on Integrated Substrate)」技術の概要を説明しよう。講演スライドが示した「InFO_SoIS」パッケージは、以下のような構造となっている。まず、再配線層(RDL)の上にSoC(System on a Chip)ダイとI/Oダイを搭載してあり、RDLによって信号線と電源線を下部に引き出す。この構造を「InFO1」と呼ぶ。下部に引き出した信号線と電源線は、マイクロバンプを通じて多層配線の樹脂基板(RDL)につながる。多層の樹脂基板の底部には、信号線と電源線を外部に引き出すバンプがInFO1よりも広いピッチでレイアウトされている。この構造を「InFO2」と呼ぶ。また樹脂基板の周縁部には反り防止用のリング(Stiffener Ring)を取り付けてある。

「InFO_SoIS」の構造図(左)と試作例(右)[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

試作した「InFO_SoIS」パッケージは、1個のSoCと、4個のI/OダイをInFO1に収容し、InFO2によって支持されている。大きさは91mm角である。シリコンダイは全て良品であり、パッケージの組み立てによる歩留まりは95%を超える。またさらに大きな110mm角の「InFO_SoIS」パッケージは100%の歩留まりを得ているとする。

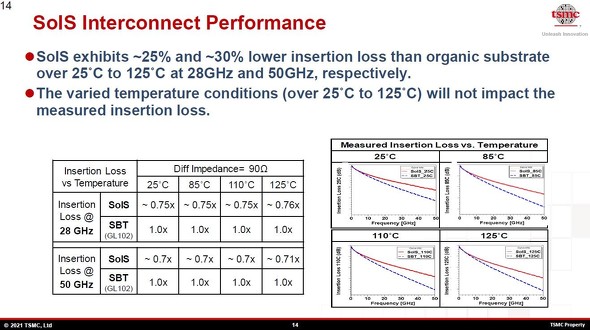

試作した「InFO_SoIS」パッケージのミリ波帯域における損失を、従来の樹脂基板(GL102)と比較した。挿入損失(温度25℃〜125℃)は28GHzで約25%、50GHzで約30%、減少した。

「InFO_SoIS」のミリ波帯域における挿入損失。従来の樹脂基板(GL102)と比較した。左下の表は28GHzおよび50GHzの相対値(従来基板を1.0としたもの)、右下のグラフは挿入損失の周波数特性[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。 欧州が欧州半導体法「European Chips Act」の策定へ

欧州が欧州半導体法「European Chips Act」の策定へ

欧州委員会委員長であるUrsula von der Leyen氏が2021年9月15日(現地時間)、一般教書演説の中で、「European Chips Act(欧州半導体法)」の策定に関する発表を行った。中国政府が半導体イノベーションに数十億米ドル規模の資金を投じていることや、米国議会が半導体の戦略的価値について合意に達したことなどを受け、EUは、主体的な最先端技術の実現を目指す法案を策定し、競争に参入していく考えを表明した。 第4世代R-Car SoCも発表、ルネサスが語る車載戦略

第4世代R-Car SoCも発表、ルネサスが語る車載戦略

ルネサス エレクトロニクスは2021年10月6日、オンラインで記者説明会を実施。同社オートモーティブソリューション事業本部の事業本部長、片岡健氏が車載事業戦略について語った。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。